### PRELIMINARY DATA SHEET

MOS INTEGRATED CIRCUIT

μ PD4516421,4516821,4516161

# 16M bit Synchronous DRAM

# Description

The uPD4516421, uPD4516821, uPD 4516161 are high-speed 16 777 216-bit synchronous dynamic random-access memories, each organized as 2 097 152-word x 4-bit x 2 banks, 1 048 576-word x 8-bit x 2 banks and 524 288-word x16-bit x 2 banks.

The synchronous DRAMs acheive high-speed data transfer using the pipeline architecture.

All inputs and outputs are syncronized with the positive edge of clock. The synchronous DRAMs conpatible with Low Voltage TTL (LVTTL).

The synchronous DRAMs are available in 400-mil, 44-pin TSOP II (x4,x8) and 400-mil, 50-pin TSOP II(x16).

#### **Features**

- Fully Synchronous Dynamic RAM, with all signals referenced to a positive clock edge

- Pulsed interface

- Possible to assert random column address in every cycle

- Dual Internal Banks controlled by A11 (Bank Select)

- Programmable burst-length (1,2,4,8 Full Page)

- Programmable wrap sequence (Sequential / Interleave)

- Programmable CAS latency (1, 2, 3)

- Automatic precharge and controlled Precharge

- CBR(Auto) refresh and self refresh

- x4, x8, x16 organization

- Single +3.3  $\pm$  0.3V power supply

- LVTTL compatible

- Byte control (x16) by LDQM and UDQM

- 2048 refresh cycles / 32ms

- Burst termination by Burst Stop command and Precharge command

The information in this document is subject to change without notice.

Ver.4.0

Document No. ID-3394

Data Published March 1994 M

Printed in Japan

© NEC Corporation 1994

# **CONTENTS**

| Ordering information                       | 03           |

|--------------------------------------------|--------------|

| Part Numbers                               | 04           |

| Pin Function                               | 05           |

| Pin Out, Pin Configuration                 | 06           |

| Commands                                   | 11           |

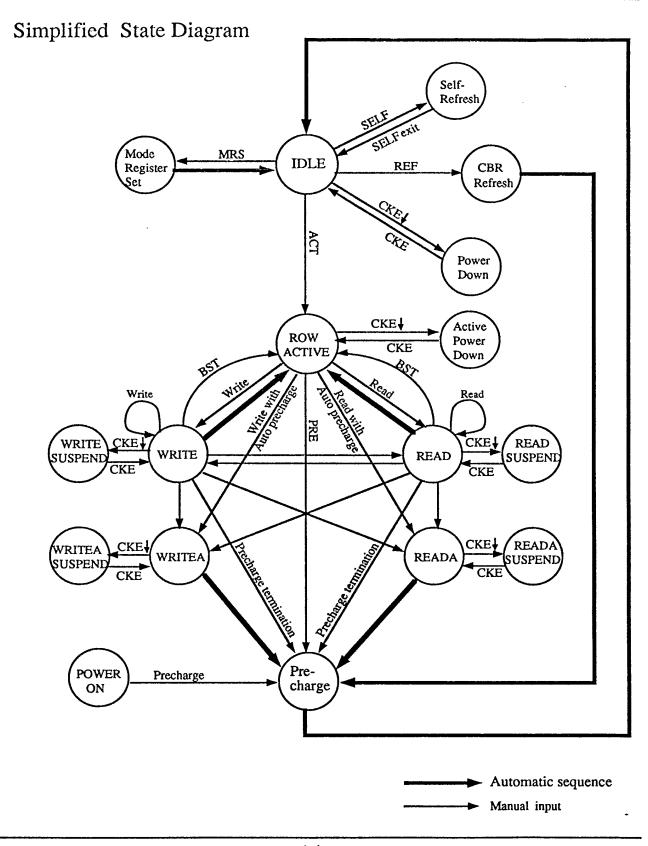

| Simplified State Diagram                   | 14           |

| Truth Table                                | 15           |

| Initialization                             | 21,41        |

| Mode Register                              | 22,40        |

| Bank-select                                | 24           |

| Auto precharge                             | 25,73        |

| Read / Write command interval              | 27           |

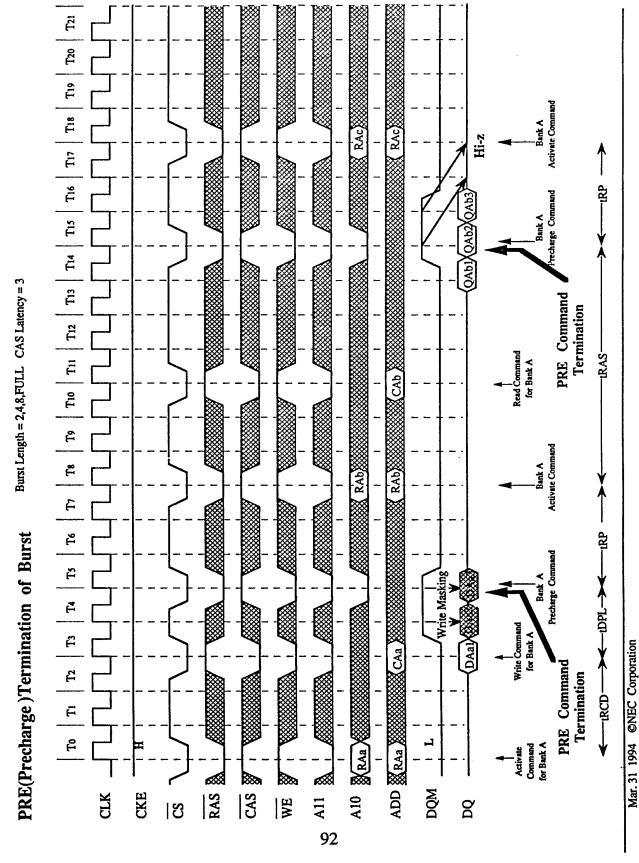

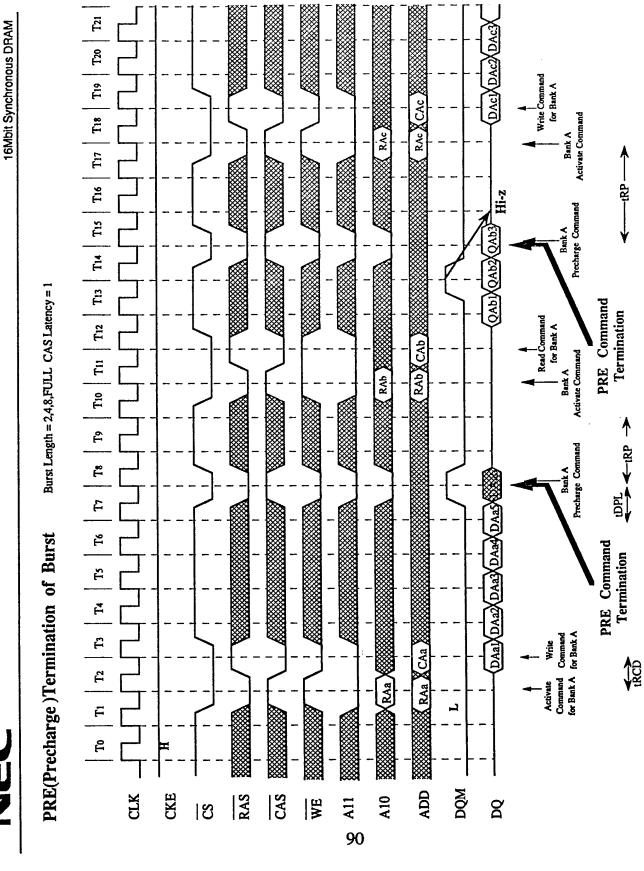

| Burst termination                          | 30,79,90     |

| Electrical Specifications                  | 33           |

| AC Parameters for Write Timing             | 37           |

| AC Parameters for Read Timing              | 38           |

| Relationship between Frequency and Latency | 39           |

| Mode Register Write                        | 40           |

| Power On Sequence & Auto Refresh           | 41           |

| CS Function                                | 42           |

| Clock Suspension in Burst Read             | 43           |

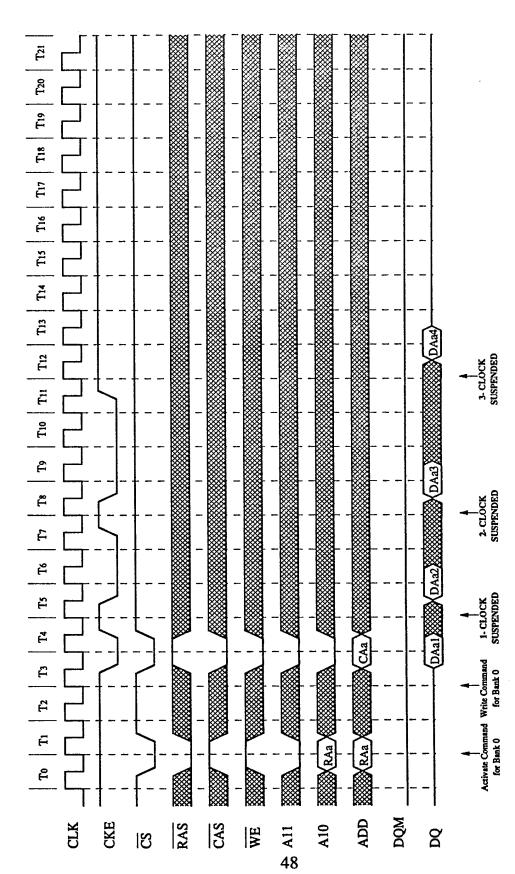

| Clock Suspension in Burst Write            | 46           |

| Power Down Mode and Clock Mask             | 49           |

| CBR Refresh                                | 50           |

| Self Refresh(entry & exit)                 | 51           |

| Random Column Read(page at same bank)      | 52           |

| Random Column Write(page at same bank)     | 55           |

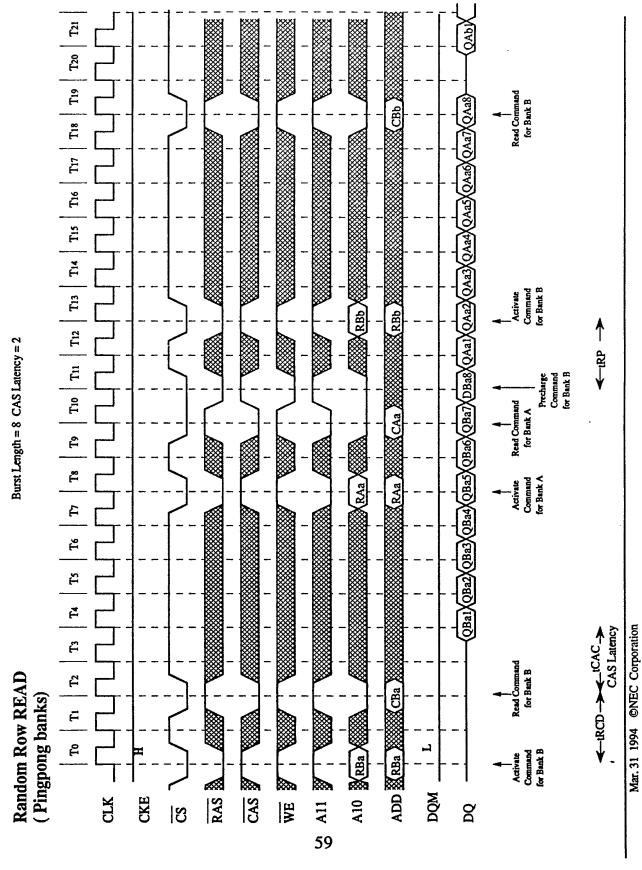

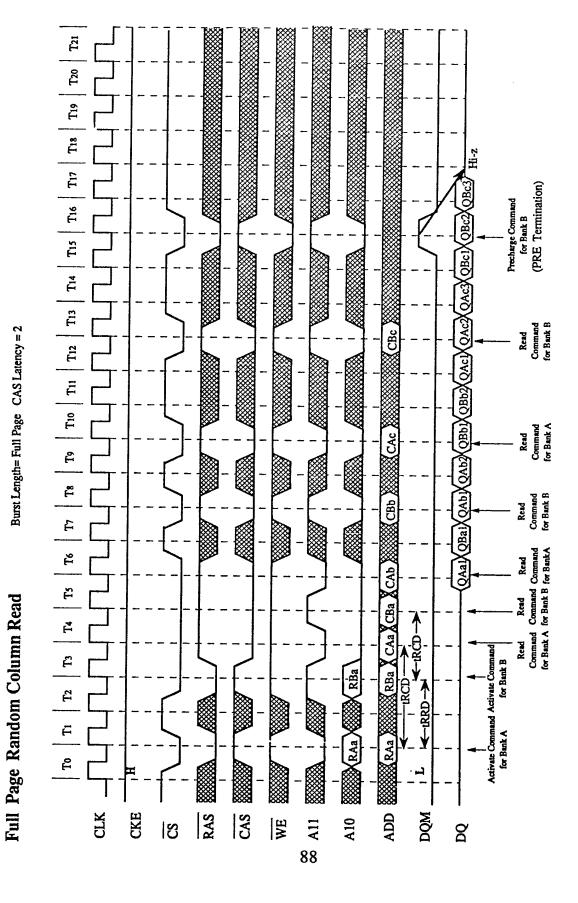

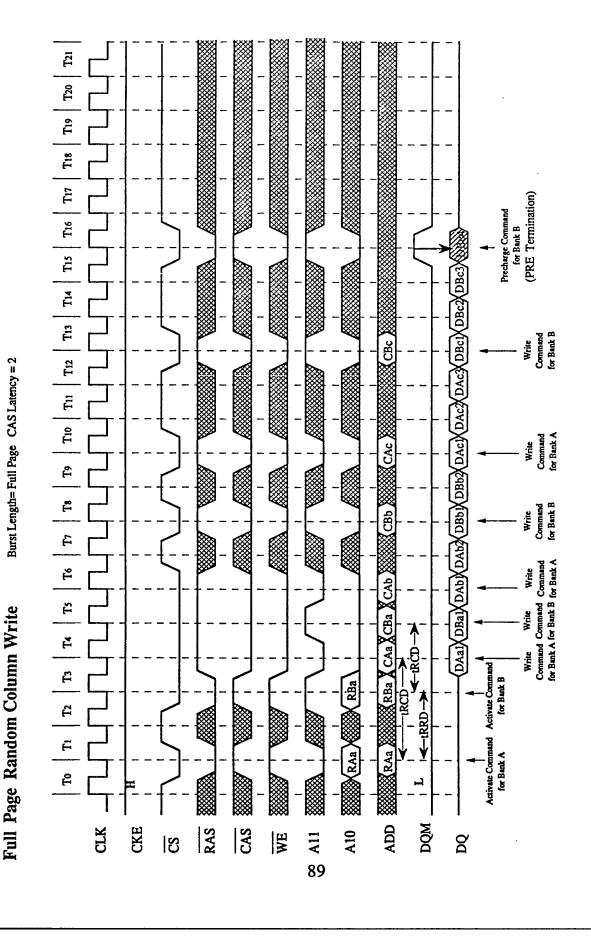

| Random Row Read(pingpong banks)            | <b>58,87</b> |

| Random Row Write(pingpong banks)           | 61           |

| READ and WRITE                             | 64           |

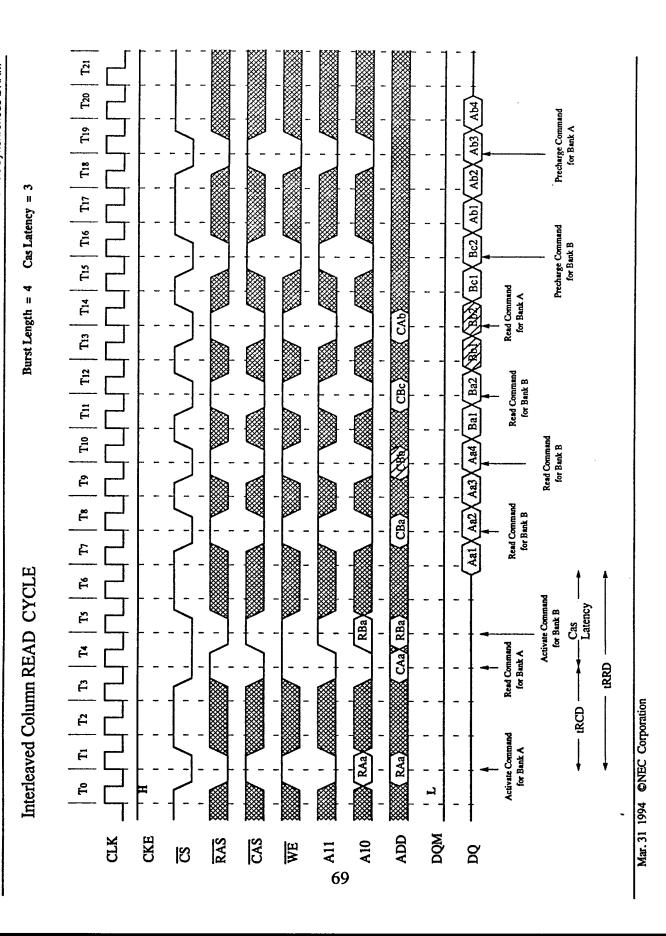

| Interleaved Column Read Cycle              | 67           |

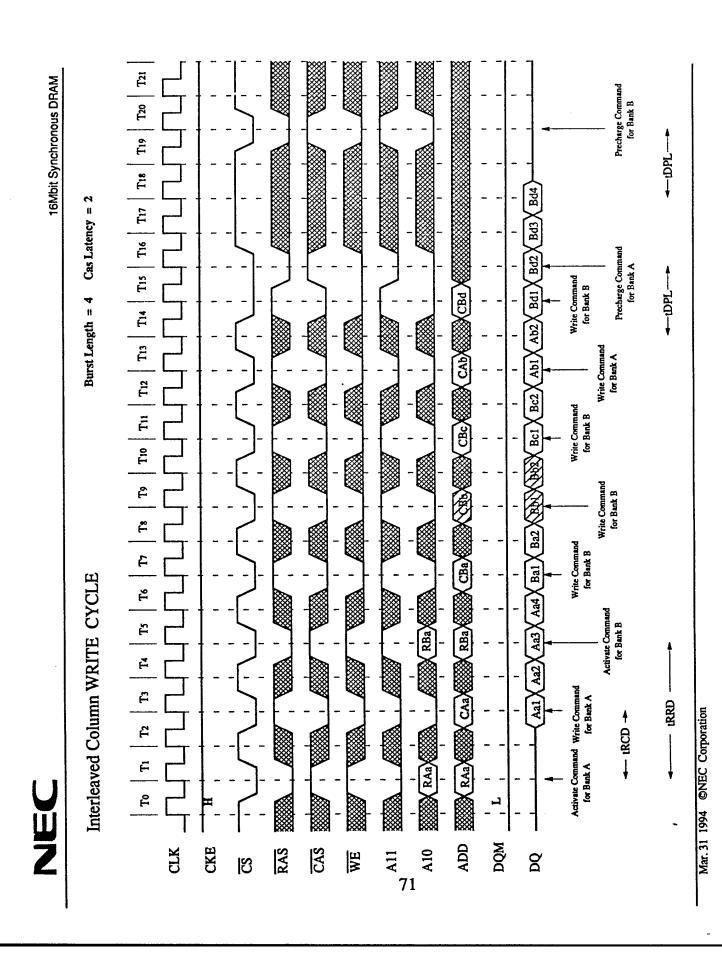

| Interleaved Column Write Cycle             | 70           |

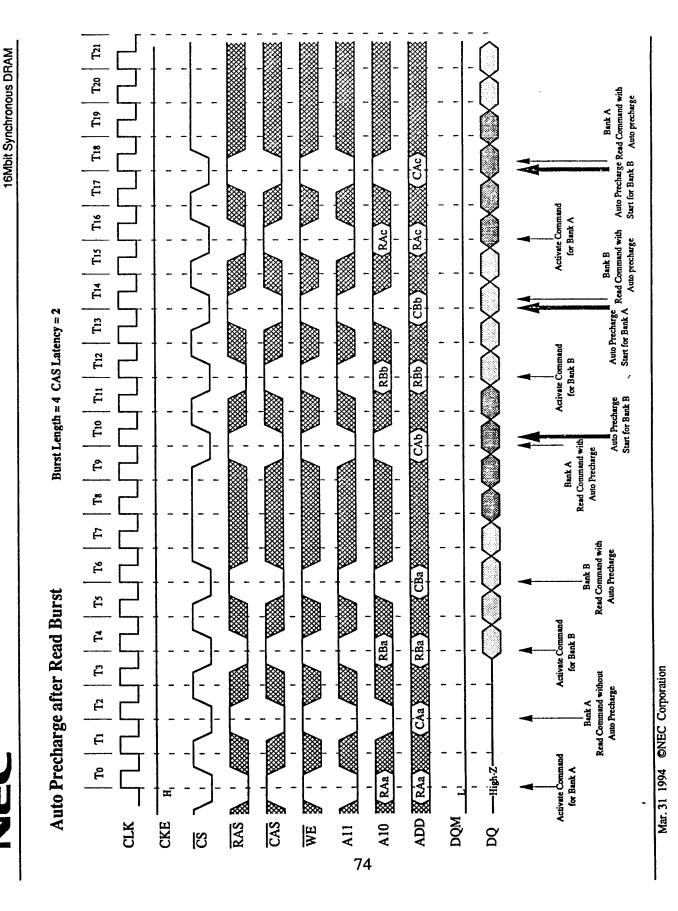

| Auto Precharge after Read Burst            | 73           |

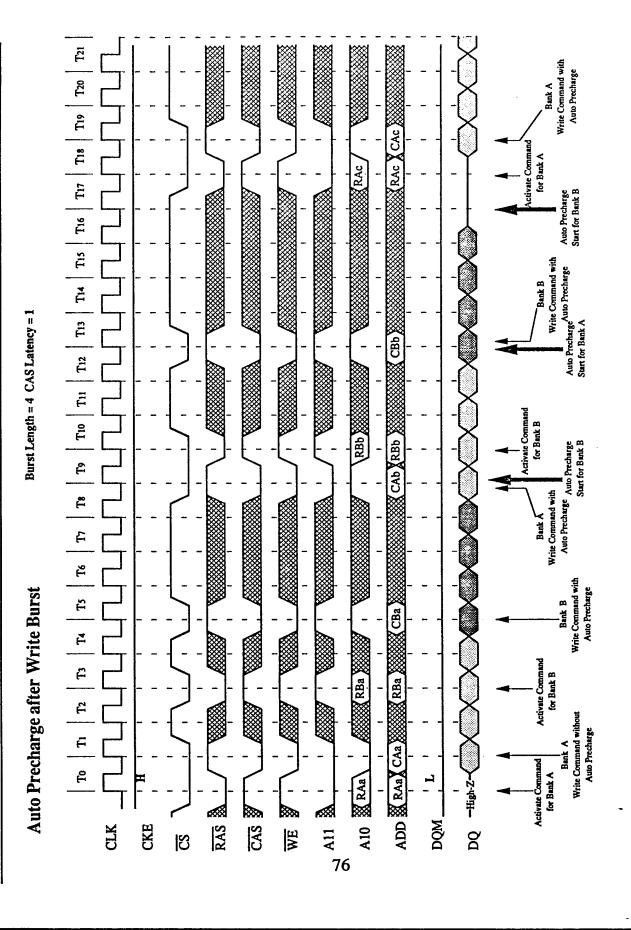

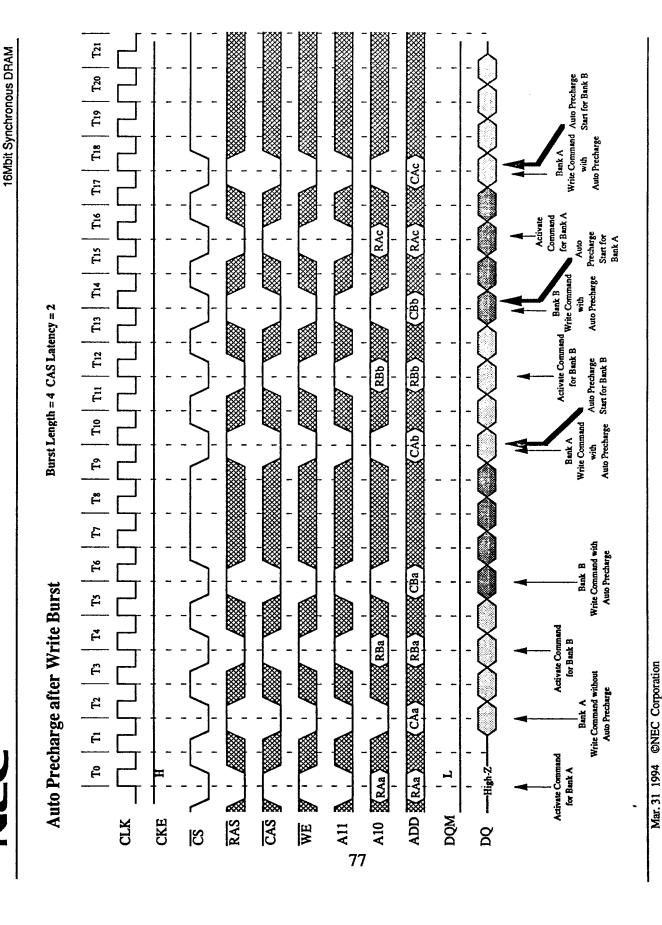

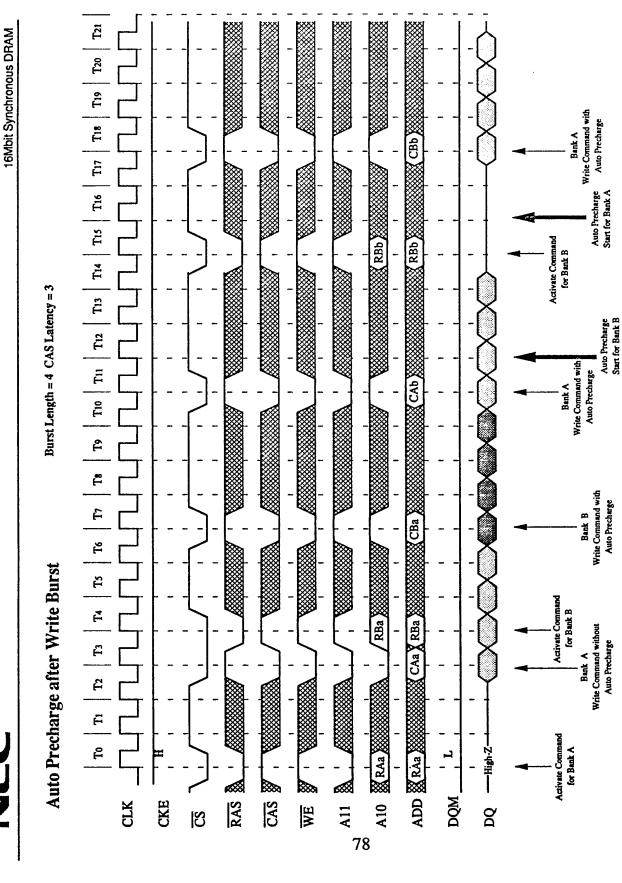

| Auto Precharge after Write Burst           | 76           |

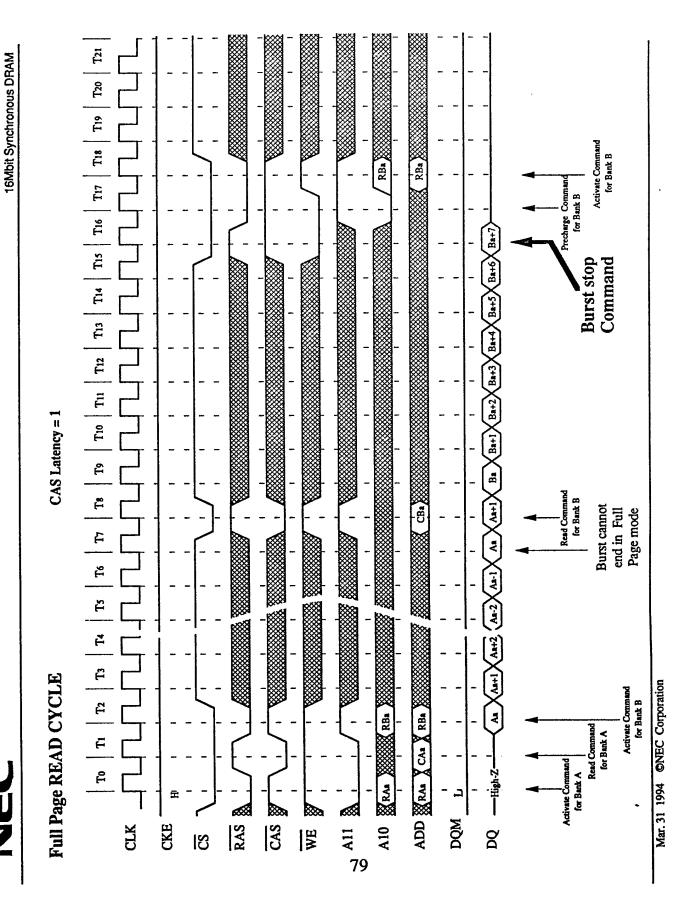

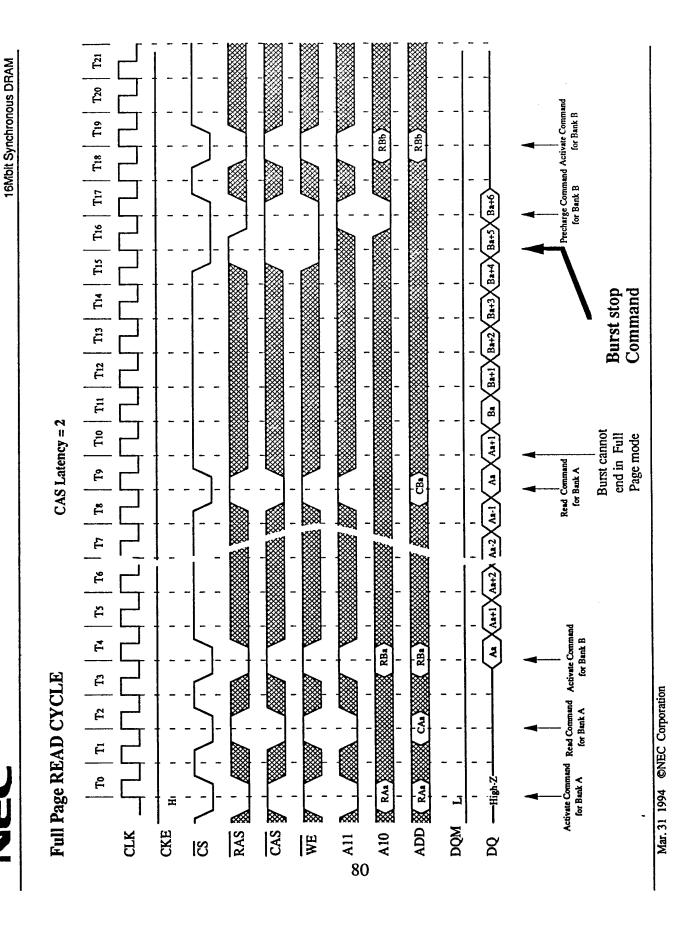

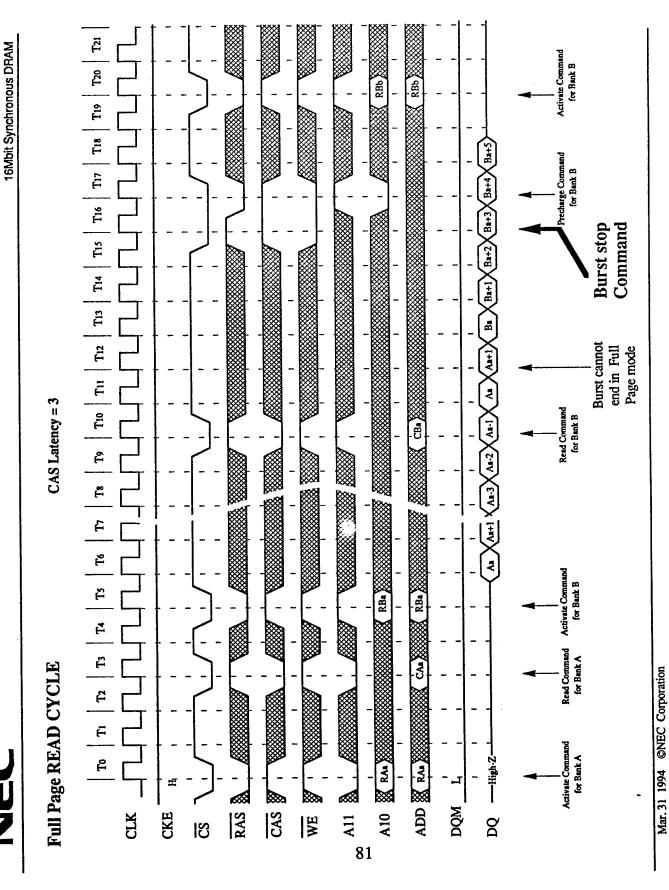

| Full Page Read Cycle                       | 79           |

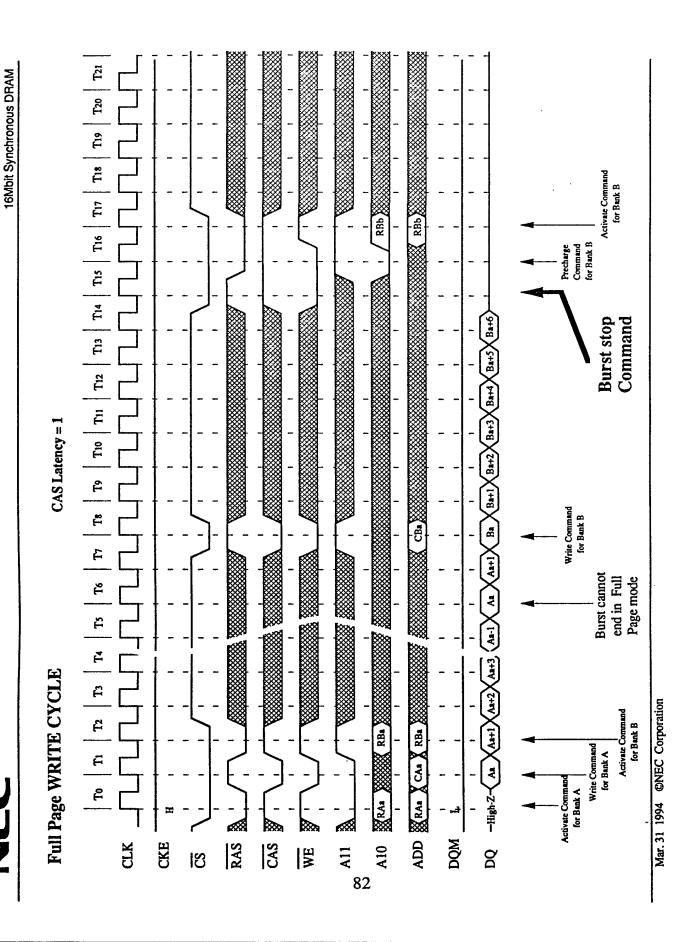

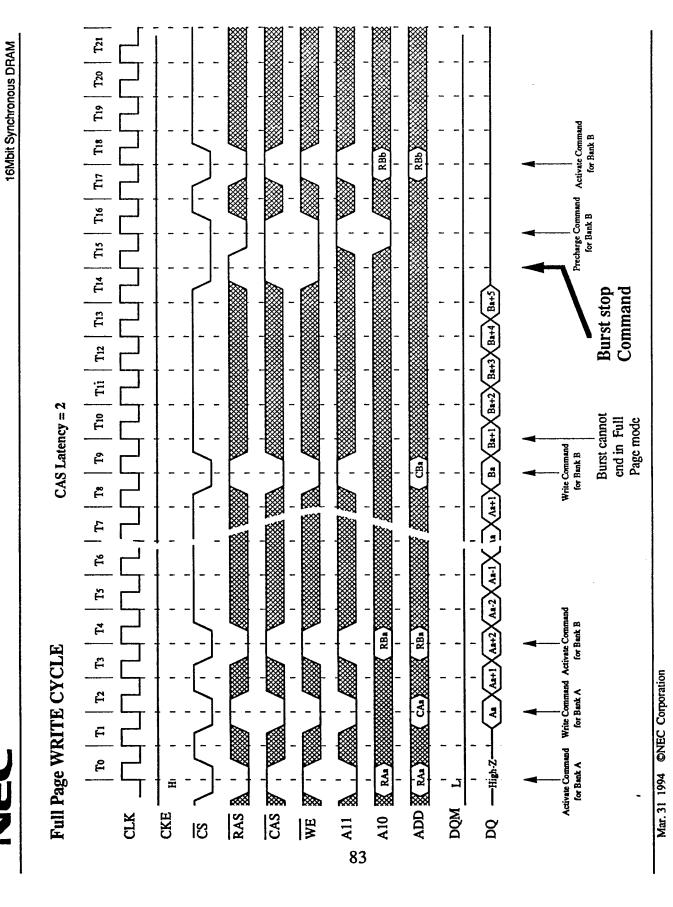

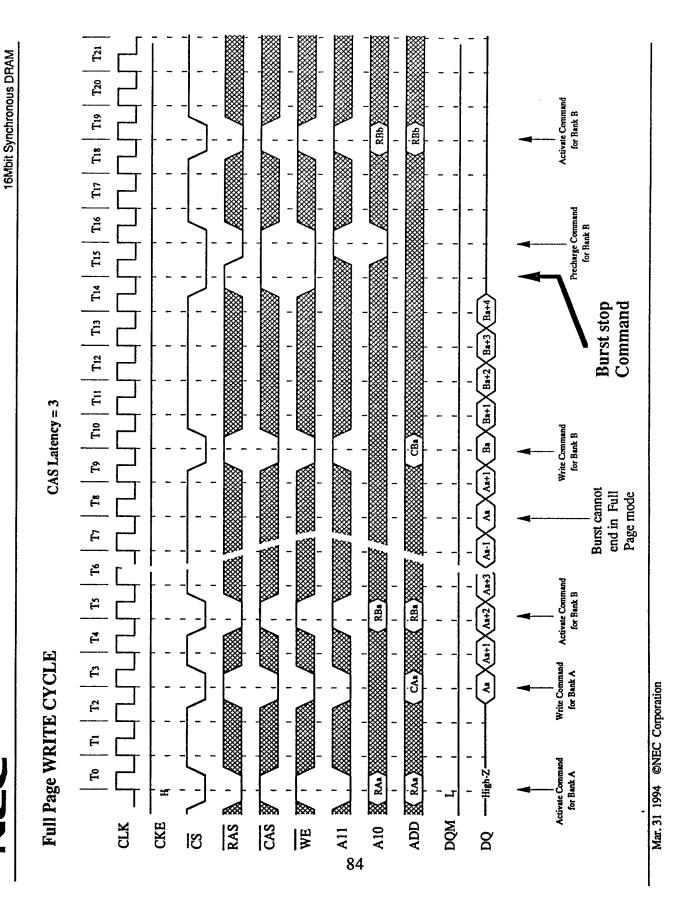

| Full Page Write Cycle                      | 82           |

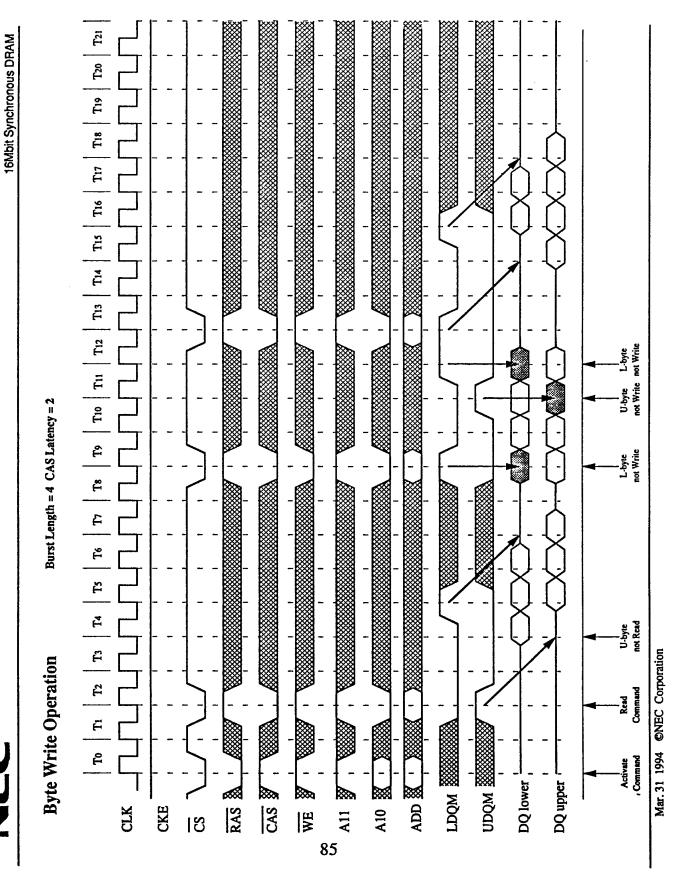

| Byte Write Operation                       | 85           |

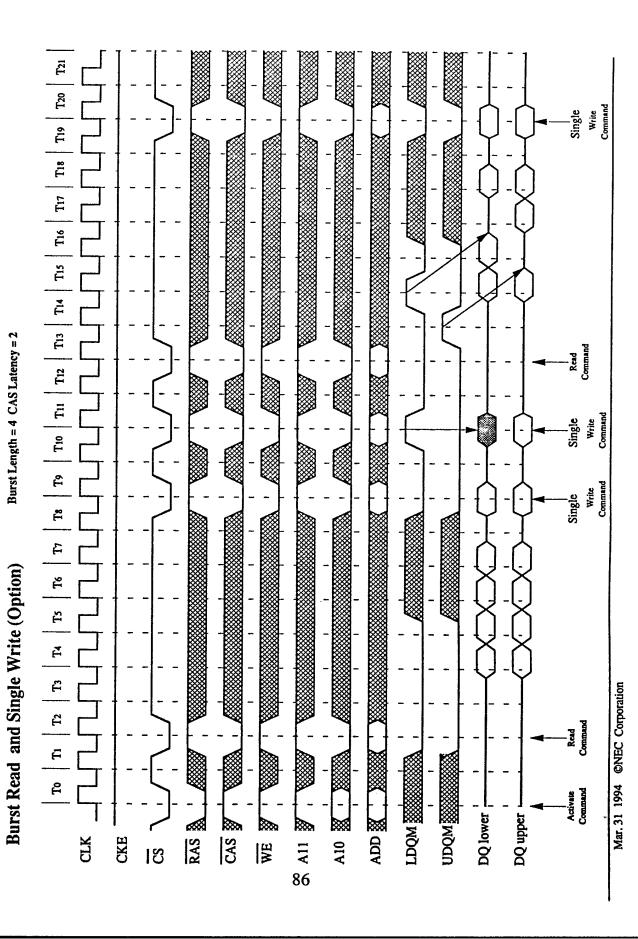

| Burst Read and Single Write(Option)        | 86           |

| Full Page Random Column Read/Write         | 88           |

| Precharge Termination of Burst             | 90           |

# Ordering information

| Part number          | Organization (word x bit x bank) | MAX.<br>Clock Frequency | Package                             |

|----------------------|----------------------------------|-------------------------|-------------------------------------|

| uPD4516421G5-A10-7JF |                                  | 100MHz                  | 44 ' DI .' TGOD/II)                 |

| uPD4516421G5-A12-7JF | $2M \times 4 \times 2$           | 83MHz                   | 44-pin Plastic TSOP(II)<br>(400mil) |

| uPD4516421G5-A13-7JF |                                  | 75MHz                   | (40011111)                          |

| uPD4516421G5-A15-7JF |                                  | 66MHz                   |                                     |

| uPD4516821G5-A10-7JF |                                  | 100MHz                  |                                     |

| uPD4516821G5-A12-7JF | 1M x 8 x 2                       | 83MHz                   | 44-pin Plastic TSOP(II)             |

| uPD4516821G5-A13-7JF | TIVI X O X Z                     | 75MHz                   | (400mil)                            |

| uPD4516821G5-A15-7JF |                                  | 66MHz                   |                                     |

| uPD4516161G5-A10-7JF |                                  | 100MHz                  |                                     |

| uPD4516161G5-A12-7JF | 512K x 16 x 2                    | 83MHz                   | 50-pin Plastic TSOP(II)             |

| uPD4516161G5-A13-7JF | 312K X 10 X 2                    | 75MHz                   | (400mil)                            |

| uPD4516161G5-A15-7JF |                                  | 66MHz                   |                                     |

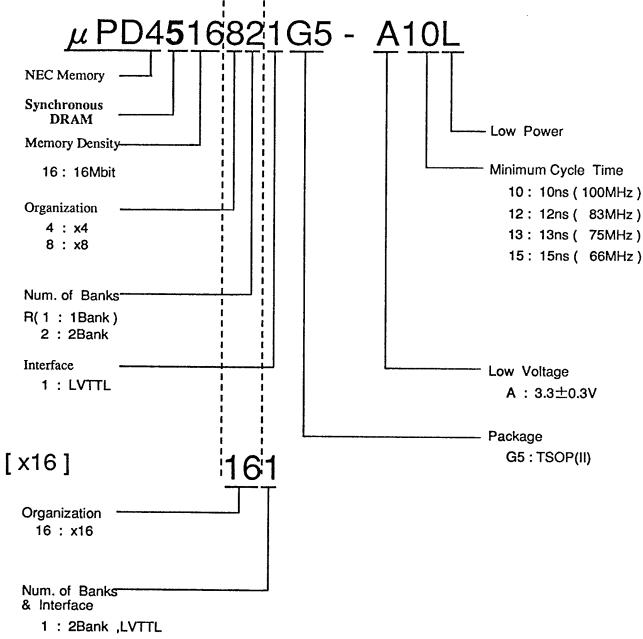

## Part Numbers

[x4, x8]

R:Reserved

Mar. 31 1994 ©NEC Corporation

| Symbol                                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK(input pin)                         | CLK is the master clock input. Other inputs signals are referenced to the CLK rising edge.                                                                                                                                                                                                                                                                                                                                                                                                  |

| CS(input pin)                          | CS low starts the command input cycle. When CS is high, commands are ignored but operations continue.                                                                                                                                                                                                                                                                                                                                                                                       |

| RAS CAS WE(input pins)                 | RAS CAS and WE have the same symbols on conventional DRAMs but different functions. For details, refer to the command table.                                                                                                                                                                                                                                                                                                                                                                |

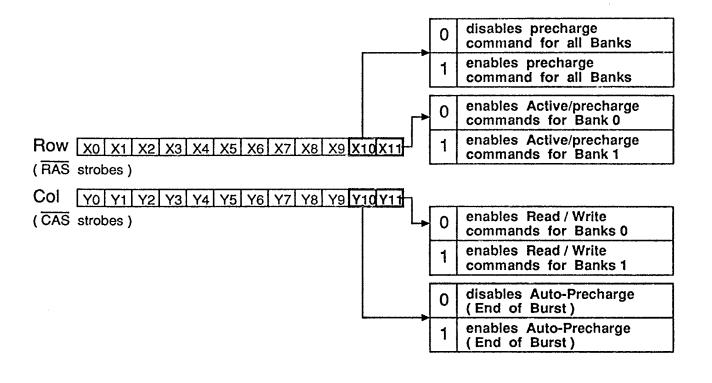

| A0 - A11(input pins)                   | Row Address is determined by A0 - A10 at the CLK(clock) rising edge in the activate command cycle. And it does not depend on the bit organization.                                                                                                                                                                                                                                                                                                                                          |

|                                        | Column Address is determined by A0 - A9 at the CLK rising edge in the read or write command cycle. It depend on the bit organi- zation. A0 - A9 for X4 device, A0 - A8 for X8 devices and A0 - A7 for X16 devices.                                                                                                                                                                                                                                                                          |

|                                        | A10 defines the precharge mode. When A10 is high in the precharge command cycle, both banks are precharged; when A10 is low, only the bank selected by A11 is precharged.                                                                                                                                                                                                                                                                                                                   |

|                                        | When A10 high in read or write command cycle, the precharge start automatically after the burst access.                                                                                                                                                                                                                                                                                                                                                                                     |

| A11(input pin)                         | All is the bank select signal (BS). In command cycle, All low selects bank A and All High selects bank B.                                                                                                                                                                                                                                                                                                                                                                                   |

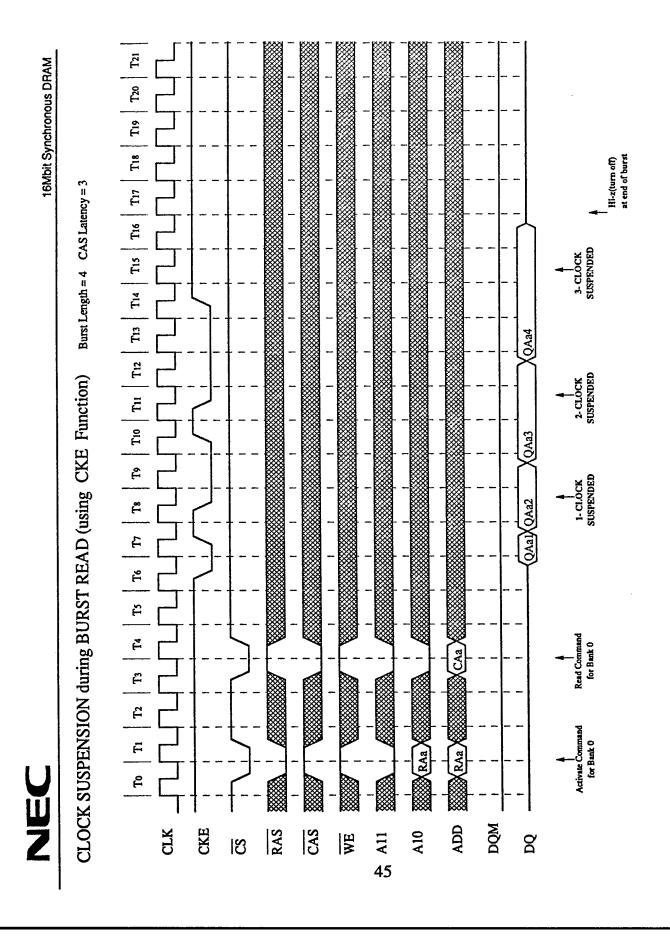

| CKE(input pin)                         | CKE determine validity of the next CLK(clock). If CKE is high ,the next CLK rising edge is valid; otherwise it is invalid. If the CLK rising edge is invalid, the internal clock is not asserted and the µPD4516XXX suspends operation.  When the µPD4516XXX is not in burst mode and CKE is negated, the device enter power-down made, during power down mode CKE must remain low.                                                                                                         |

| DQM , DQMU , DQML (input pin)          | DQM controls I/O buffers .In X16 products ,DQMU and DQML control upper byte and lower byte I/O buffers,respectively.  In read mode, DQM control the output buffers the same as a conventional OE pin. Respectively, DQM high and DQM low turn the output buffers off and on.  The DQM latency for the read is two clocks.  In write mode,DQM controls the word mask. Input data is written to the memory cell if DQM is low but not if DQM is high.  The DQM latency for the write is zero. |

| I/O0 - I/O15<br>(input/output pins)    | I/O pins have the same function as I/O pins on a conventional DRAM.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Vcc, Vss, VccQ, VssQ<br>(power supply) | Vcc and Vss are power supply pins for internal circuits.VccQ and VssQ are power supply pins for the output buffers.                                                                                                                                                                                                                                                                                                                                                                         |

#### PIN OUT (4Mx4)

#### LVTTL

| Vcc  | 1  |   | 44 | Vss  |

|------|----|---|----|------|

| NC   | 2  |   | 43 | NC   |

| VssQ | 3  |   | 42 | VssQ |

| DQ0  | 4  |   | 41 | DQ3  |

| VccQ | 5  |   | 40 | VccQ |

| NC   | 6  | ' | 39 | NC   |

| VssQ | 7  |   | 38 | VssQ |

| DQ1  | 8  |   | 37 | DQ2  |

| VccQ | 9  |   | 36 | VccQ |

| NC   | 10 |   | 35 | NC   |

| NC   | 11 |   | 34 | NC   |

| WE   | 12 |   | 33 | DQM  |

| CAS  | 13 |   | 32 | CLK  |

| RAS  | 14 |   | 31 | CKE  |

| CS   | 15 |   | 30 | NC   |

| A11  | 16 |   | 29 | A9   |

| A10  | 17 |   | 28 | A8   |

| A0   | 18 |   | 27 | A7   |

| A1   | 19 |   | 26 | A6   |

| A2   | 20 |   | 25 | A5   |

| A3   | 21 |   | 24 | A4   |

| Vcc  | 22 |   | 23 | Vss  |

400mil 44Pin 0.8mmTSOP(II)

#### Pin Identification

| Name           | Function               |

|----------------|------------------------|

| A0 to A11      | Address Inputs         |

| (A0 to A11     | Row Address Inputs)    |

| (A0 to A9, A11 | Column Address Inputs) |

| DQ0 to DQ3     | Data Inputs/Outputs    |

| CLK            | System Clock Input     |

| CKE            | Clock Enable           |

| <u>CS</u>      | Chip Select            |

| RAS            | Row Address Strobe     |

| CAS            | Col Address Strobe     |

| Function              |

|-----------------------|

| Write Enable          |

| DQ Mask Enable        |

| Supply Voltage        |

| Ground                |

| Supply Voltage for DQ |

| Ground for DQ         |

| No connection         |

|                       |

#### PIN OUT (2Mx8)

#### LVTTL

|      |    |         | <del></del> , |      |

|------|----|---------|---------------|------|

| Vcc  | 1  |         | 44            | Vss  |

| DQ0  | 2  |         | 43            | DQ7  |

| VssQ | 3  |         | 42            | VssQ |

| DQ1  | 4  |         | 41            | DQ6  |

| VccQ | 5  |         | 40            | VccQ |

| DQ2  | 6  |         | 39            | DQ5  |

| VssQ | 7  |         | 38            | VssQ |

| DQ3  | 8  |         | 37            | DQ4  |

| VccQ | 9  |         | 36            | VccQ |

| NC   | 10 |         | 35            | NC   |

| NC   | 11 |         | 34            | NC   |

| WE   | 12 |         | 33            | DQM  |

| CAS  | 13 |         | 32            | CLK  |

| RAS  | 14 |         | 31            | CKE  |

| CS   | 15 |         | 30            | NC   |

| A11  | 16 |         | 29            | A9   |

| A10  | 17 |         | 28            | A8   |

| A0   | 18 |         | 27            | A7   |

| A1   | 19 |         | 26            | A6   |

| A2   | 20 |         | 25            | A5   |

| A3   | 21 |         | 24            | A4   |

| Vcc  | 22 | <u></u> | 23            | Vss  |

400mil 44Pin 0.8mmTSOP(II)

#### Pin Identification

| Name           | Function               |

|----------------|------------------------|

| A0 to A11      | Address Inputs         |

| (A0 to A11     | Row Address Inputs)    |

| (A0 to A8, A11 | Column Address Inputs) |

| DQ0 to DQ7     | Data Inputs/Outputs    |

| CLK            | System Clock Input     |

| CKE            | Clock Enable           |

| <u>CS</u>      | Chip Select            |

| RAS            | Row Address Strobe     |

| CAS            | Col Address Strobe     |

| Name | Function              |

|------|-----------------------|

| WE   | Write Enable          |

| DQM  | DQ Mask Enable        |

| Vcc  | Supply Voltage        |

| Vss  | Ground                |

| VccQ | Supply Voltage for DQ |

| VssQ | Ground for DQ         |

| NC   | No connection         |

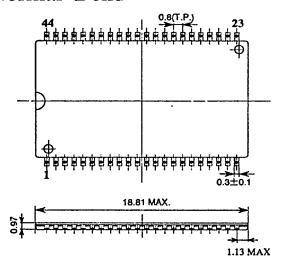

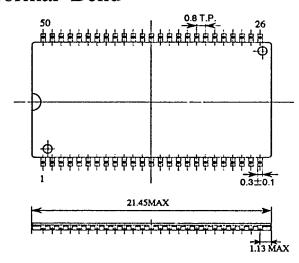

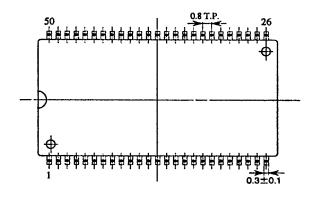

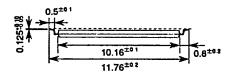

# PIN CONFIGURATION

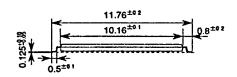

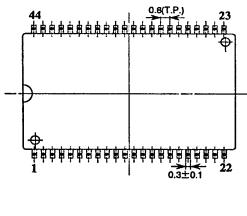

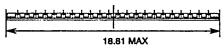

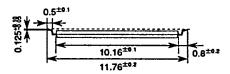

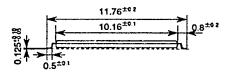

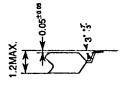

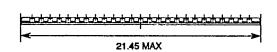

X4/X8/X9/

44pin 400mil TSOP (TypeII) (unit:mm)

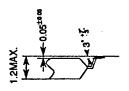

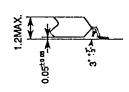

# Normal Bend

# Reverse Bend

#### PIN OUT (1Mx16)

#### LVTTL

|      |    | <br> |      |

|------|----|------|------|

| Vcc  | 1  | 50   | Vss  |

| DQ0  | 2  | 49   | DQ15 |

| DQ1  | 3  | 48   | DQ14 |

| VssQ | 4  | 47   | VssQ |

| DQ2  | 5  | 46   | DQ13 |

| DQ3  | 6  | 45   | DQ12 |

| VccQ | 7  | 44   | VccQ |

| DQ4  | 8  | 43   | DQ11 |

| DQ5  | 9  | 42   | DQ10 |

| VssQ | 10 | 41   | VssQ |

| DQ6  | 11 | 40   | DQ9  |

| DQ7  | 12 | 39   | DQ8  |

| VccQ | 13 | 38   | VccQ |

| LDQM | 14 | 37   | NC   |

| WE   | 15 | 36   | UDQM |

| CAS  | 16 | 35   | CLK  |

| RAS  | 17 | 34   | CKE  |

| CS   | 18 | 33   | NC   |

| A11  | 19 | 32   | A9   |

| A10  | 20 | 31   | A8   |

| A0   | 21 | 30   | A7   |

| A1   | 22 | 29   | A6   |

| A2   | 23 | 28   | A5   |

| A3   | 24 | 27   | A4   |

| Vcc  | 25 | 26   | Vss  |

#### 400mil 50Pin 0.8mmTSOP(II)

#### Pin Identification

| Name           | Function               |

|----------------|------------------------|

| A0 to A11      | Address Inputs         |

| (A0 to A11     | Row Address Inputs)    |

| (A0 to A7, A11 | Column Address Inputs) |

| DQ0 to DQ15    | Data Inputs/Outputs    |

| CLK            | System Clock Input     |

| CKE            | Clock Enable           |

| <u>CS</u>      | Chip Select            |

| RAS            | Row Address Strobe     |

| CAS            | Col Address Strobe     |

| Function              |

|-----------------------|

| Write Enable          |

| DQ Mask Enable        |

| Supply Voltage        |

| Ground                |

| Supply Voltage for DQ |

| Ground for DQ         |

| No connection         |

|                       |

# PIN CONFIGURATION

X16/X18

50pin 400mil TSOP (TypeII) (unit:mm)

# Normal Bend

# Reverse Bend

#### **Commands**

Mode register set command

(CS, RAS, CAS, WE = Low)

$\mu PD4516XXX$  has a mode register that define how the device operates. In this command, A0 - A11 are the data input pins. After power-on, the mode register set command must be executed to initialize the device.

The mode register can be set only when both banks are in idle state. During the two cycles following this command,  $\mu PD4516XXX$  cannot accept any other commands.

Fig.1 Mode register set command

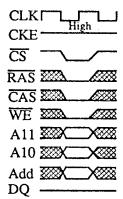

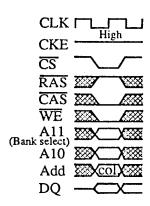

Row activate command

$(\overline{CS}, \overline{RAS} = Low, \overline{CAS}, \overline{WE} = High)$

μPD4516XXX has two banks, each with 2048 rows. This command activates the bank selected by A11(BS) and a row address selected by A0 - A10.

The command corresponds to a conventional DRAM's falling RAS signal.

Fig.2 Row address strobe and bank active command

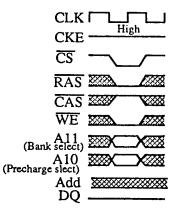

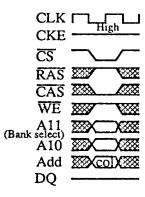

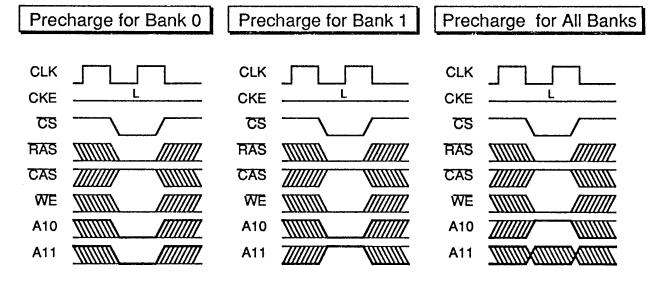

Precharge command

$(\overline{CS}, \overline{RAS}, \overline{WE} = Low, \overline{CAS} = High)$

This command begins precharge operation of the bank selected by A11(BS) and A10. When A10 is High, both banks are precharged, regardless of A11. When A10 is Low, only the bank selected by A11 is precharged. A11 low selects bank A and A11 high selects bank B.

After this command,  $\mu PD4516XXX$  can't accept the activate command to the precharging bank during  $t_{RP}$  (precharge to activate command period) .

The command corresponds to a conventional DRAM's rising RAS signal.

Fig.3 Precharge command

# NEC

#### Column Address and Write command

$(\overline{CS}, \overline{CAS}, \overline{WE} = Low, \overline{RAS} = High)$

If the mode register is in the burst write mode, this command sets the burst start address given by the column address to begin the burst write operation. The first write data must be input with this write operation. The first write data in burst mode can input with this command with subsequent data on following clocks.

Fig.4 Column Address and Write command

#### Column address and Read command

$(\overline{CS}, \overline{CAS} = Low, \overline{RAS}, \overline{WE} = High)$

This command sets the burst start address given by the column address.

Read data is available after CAS Latency requirements have been met.

Fig.5 Column address and Read command

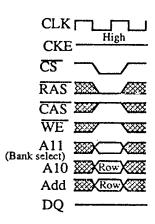

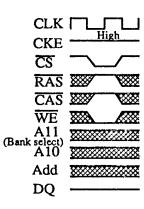

#### CBR (Auto) refresh command

$(\overline{CS}, \overline{RAS}, \overline{CAS} = Low, \overline{WE}, CKE = High)$

This command is a request to begin the CBR refresh operation. The refresh address and the bank select address are generated internally. Before executing CBR refresh, both banks must be precharged.

After this cycle, both banks will be in the idle (precharge) state and ready for a row activate command.

During the period (from refresh command to refresh or activate command), µPD4516XXX cannot accept any other command.

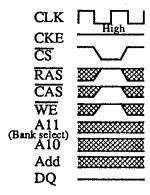

|       | CLK                   |               | gh         |

|-------|-----------------------|---------------|------------|

|       | CKE                   |               | <u>EII</u> |

|       | <u>CS</u>             | _             |            |

|       | RAS                   |               |            |

|       | CAS                   |               | <i>[</i>   |

|       | WE                    |               | V          |

| (Rank | A11<br>select)<br>A10 | W. W.         |            |

| (Dalk | A10'                  | <b>******</b> | /////      |

|       | Add                   | <b>*****</b>  |            |

|       | DQ                    |               |            |

Fig.6 Auto refresh command

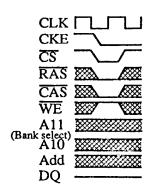

Self - refresh Entry command

$(\overline{CS}, \overline{RAS}, \overline{CAS}, \overline{CKE} = Low, \overline{WE} = High)$

After the command execution, self refresh operation continues while CKE remains low. When CKE goes high , the  $\mu PD4516XXX$  exits the self-refresh mode.

During self- refresh mode, refresh interval and refresh operation are preformed internally, so there is no need for external control. Before executing self-refresh, both banks must be precharged.

Fig.7 Self refresh Entry command

**Burst stop command**

$(\overline{CS}, \overline{WE} = Low, \overline{RAS}, \overline{CAS} = High)$

This command terminates the current burst operation.

Fig.8 Burst stop command in Full Page mode

No Operation

$(\overline{CS} = Low, RAS, CAS, WE = High)$

This command is not a execution command. No operations begin or terminate by this command.

Fig.9 No Operation

Mar. 31 1994 © NEC Corporation

14

# Command truth table

| Tomation                  | Complete | C   | KE | CS | RAS | CAS | WE | A11 | A10 | A9 |

|---------------------------|----------|-----|----|----|-----|-----|----|-----|-----|----|

| Function                  | Symbol   | n-1 | n  | L3 | KAS | CAS |    | AII | Alo | -0 |

| Device Deselect           | DESL     | Н   | Х  | Н  | х   | х   | х  | х   | х   | x  |

| No Operation              | NOP      | Н   | х  | L  | Н   | Н   | Н  | х   | х   | х  |

| Burst stop                | BST      | Н   | х  | L  | Н   | Н   | L  | х   | х   | х  |

| Read                      | READ     | Н   | х  | L  | Н   | L   | H  | V   | L   | V  |

| Read with Auto Precharge  | READA    | Н   | х  | L  | Н   | L   | Н  | V   | Н   | V  |

| Write                     | WRIT     | Н   | х  | L  | Н   | L   | L  | V   | L   | v  |

| Write with Auto Precharge | WRITA    | Н   | Х  | L  | н   | L   | L  | V   | Н   | V  |

| Bank Activate             | ACT      | Н   | Х  | L  | L   | н   | Н  | V   | V   | V  |

| Precharge select Bank     | PRE      | Н   | х  | L  | L   | Н   | L  | V   | L   | Х  |

| Precharge All Banks       | PALL     | Н   | х  | L  | L   | Н   | L  | х   | Н   | х  |

| Mode register set         | MRS      | Н   | х  | L  | L   | L   | L  | L   | L   | V  |

#### DQM truth table

| Function                                  | Symbol | CI  | Œ | DQM |   |  |  |

|-------------------------------------------|--------|-----|---|-----|---|--|--|

| , unotion                                 |        | n-1 | n | U   | L |  |  |

| Data Write / Output Enable                | ENB    | Н   | Х | X L |   |  |  |

| Data Mask / Output Disable                | MASK   | Н   | х | Н   |   |  |  |

| Upper byte Write Enable / Output Enable   | ENBU   | Н   | х | L   | х |  |  |

| Lower byte Write Enable / Output Enable   | ENBL   | Н   | х | х   | L |  |  |

| Upper byte Write Inhibit / Output Disable | MASKU  | Н   | X | Н   | х |  |  |

| Lower byte Write Inhibit / Output Disable | MASKL  | Н   | х | х   | Н |  |  |

#### CKE truth table

| Current state | Function                 | Sym  | CKE |   | <del>cs</del> | RAS | CAS | WE | Add |

|---------------|--------------------------|------|-----|---|---------------|-----|-----|----|-----|

| Current state | runction                 | bol  | n-1 | n | CS            | KAS | CAS | WE | Au  |

| Activating    | Clock Suspend Mode Entry |      | Н   | L | х             | х   | х   | х  | х   |

| Any           | Clock Suspend            |      | L   | L | х             | Х   | Х   | Х  | Х   |

| Clock suspend | Clock Suspend Mode Exit  |      | L   | Н | x             | х   | х   | х  | х   |

| Idle          | CBR Refresh Command      | REF  | Н   | Н | L             | L   | L   | Н  | х   |

| Idle          | Self Refresh Entry       | SELF | Н   | L | L             | L   | L   | Н  | х   |

| Self Refresh  | Self Refresh Exit        |      | L   | Н | L             | Н   | Н   | Н  | Х   |

| Self Reffesh  | Sen Renesh Ball          |      | L   | Н | Н             | Х   | х   | х  | Х   |

| Idle          | Power Down Entry         |      | Н   | L | х             | Х   | Х   | х  | х   |

| Power Down    | Power Down Exit          |      | L   | Н | x             | х   | х   | х  | х   |

H: High level, L: Low level

X: High or Low level (Don't care), V: Valid Data input

# Operative command table 1

| Current<br>State | cs | RAS | CAS | WE | Add       | Command    | Action                                     | Note |

|------------------|----|-----|-----|----|-----------|------------|--------------------------------------------|------|

| Idle             | Н  | х   | x   | х  | х         | DESL       | Nop or Power Down                          | 5    |

|                  | L  | Н   | Н   | х  | x         | NOP or BST | Nop or Power Down                          | 5    |

|                  | L  | Н   | L   | Н  | BA,CA,A10 | READ/READA | ILLEGAL                                    | 3    |

|                  | L  | Н   | L   | L  | BA,CA,A10 | WRIT/WRITA | ILLEGAL                                    | 3    |

|                  | L  | L   | Н   | Н  | BA,RA     | ACT        | Row Active                                 |      |

|                  | L  | L   | Н   | L  | BA,A10    | PRE/PALL   | Nop                                        |      |

|                  | L  | L   | L   | Н  | х         | REF/SELF   | Refresh or Self Refresh                    | 6    |

|                  | L  | L   | L   | L  | Op-Code   | MRS        | Mode Register Access                       |      |

| Row              | Н  | x   | x   | х  | х         | DESL       | Nop                                        |      |

| Active           | L  | Н   | Н   | х  | х         | NOP or BST | Nop                                        |      |

|                  | L  | Н   | L   | Н  | BA,CA,A10 | READ/READA | Begin Read:Determine AP                    | 11   |

|                  | L  | Н   | L   | L  | BA,CA,A10 | WRIT/WRITA | Begin Write:Determine AP                   | 11   |

|                  | L  | L   | Н   | Н  | BA,RA     | ACT        | ILLEGAL                                    | 3    |

|                  | L  | L   | Н   | L  | BA,A10    | PRE/PALL   | Precharge                                  | 8    |

|                  | L  | L   | L   | Н  | х         | REF/SELF   | ILLEGAL                                    |      |

|                  | L  | L   | L   | L  | Op-Code   | MRS        | ILLEGAL                                    |      |

| Read             | Н  | х   | x   | х  | х         | DESL       | Continue Burst to End->Row Active          |      |

|                  | L  | Н   | Н   | Н  | х         | NOP        | Continue Burst to End->Row Active          |      |

|                  | L  | Н   | Н   | L  | х         | BST        | Burst Stop ->Row Active                    | ·    |

|                  | L  | Н   | L   | Н  | BA,CA,A10 | READ/READA | Term Burst, New Read: Determine AP         | 9    |

|                  | L  | Н   | L   | L  | BA,CA,A10 | WRIT/WRITA | Term Burst, Start Write: Determine AP      | 4,9  |

|                  | L  | L   | Н   | Н  | BA,RA     | ACT        | ILLEGAL                                    | 3    |

|                  | L  | L   | Н   | L  | BA,A10    | PRE/PALL   | Term Burst, Precharging                    |      |

|                  | L  | L   | L   | Н  | х         | REF/SELF   | ILLEGAL                                    |      |

|                  | L  | L   | L   | L  | Op-Code   | MRS        | ILLEGAL                                    |      |

| Write            | Н  | х   | x   | x  | х         | DESL       | Continue Burst to End->Write<br>Recovering |      |

|                  | L  | Н   | Н   | H  | х         | NOP        | Continue Burst to End->Write<br>Recovering |      |

|                  | L  | Н   | Н   | L  | х         | BST        | Burst Stop ->Row Active                    |      |

|                  | L  | Н   | L   | Н  | BA,CA,A10 | READ/READA | Term Burst, Start Read: Determine AP       | 4,9  |

|                  | L  | Н   | L   | L  | BA,CA,A10 | WRIT/WRITA | Term Burst, New Write: Determine AP        | 9    |

|                  | L  | L   | Н   | Н  | BA,RA     | ACT        | ILLEGAL                                    | 3    |

|                  | L  | L   | Н   | L  | BA,A10    | PRE/PALL   | Term Burst, Precharging                    | 10   |

|                  | L  | L   | L   | Н  | х         | REF/SELF   | ILLEGAL                                    |      |

|                  | L  | L   | L   | L  | Op-Code   | MRS        | ILLEGAL                                    |      |

# Operative command table 1 (Continued)

| Current<br>State   | cs | RAS | CAS | WE | Add       | Command    | Action                                                         | Note |  |

|--------------------|----|-----|-----|----|-----------|------------|----------------------------------------------------------------|------|--|

| Read with          | Н  | х   | х   | x  | X         | DESL       | Continue Burst to End->Precharging                             |      |  |

| Auto<br>Precharge  | L  | Н   | Н   | н  | х         | NOP        | Continue Burst to End->Precharging                             |      |  |

| Tromago            | L  | Н   | Н   | L  | x         | BST        | ILLEGAL                                                        |      |  |

|                    | L  | Н   | L   | Н  | BA,CA,A10 | READ/READA | ILLEGAL                                                        |      |  |

|                    | L  | Н   | L   | L  | BA,CA,A10 | WRIT/WRITA | ILLEGAL                                                        |      |  |

|                    | L  | L   | Н   | Н  | BA,RA     | ACT        | ILLEGAL                                                        | 3    |  |

|                    | L  | L   | Н   | L  | BA,A10    | PRE/PALL   | ILLEGAL                                                        | 3    |  |

|                    | L  | L   | L   | Н  | х         | REF/SELF   | ILLEGAL                                                        |      |  |

|                    | L  | L   | L   | L  | Op-Code   | MRS        | ILLEGAL                                                        |      |  |

| Write with<br>Auto | Н  | x   | х   | х  | х         | DESL       | Continue Burst to End->Write<br>Recovering with Auto Precharge |      |  |

| Precharge          | L  | н   | н   | Н  | х         | NOP        | Continue Burst to End->Write<br>Recovering with Auto Precharge |      |  |

|                    | L  | Н   | Н   | L  | х         | BST        | ILLEGAL                                                        |      |  |

|                    | L  | Н   | L   | Н  | BA,CA,A10 | READ/READA | ILLEGAL                                                        |      |  |

| ļ                  | L  | Н   | L   | L  | BA,CA,A10 | WRIT/WRITA | ILLEGAL                                                        |      |  |

|                    | L  | L   | Н   | Н  | BA,RA     | ACT        | ILLEGAL                                                        | 3    |  |

|                    | L  | L   | Н   | L  | BA,A10    | PRE/PALL   | ILLEGAL                                                        | 3    |  |

|                    | L  | L   | L   | н  | x         | REF/SELF   | ILLEGAL                                                        |      |  |

|                    | L  | L   | L   | L  | Op-Code   | MRS        | ILLEGAL                                                        |      |  |

| Precharg-          | Н  | х   | x   | x  | х         | DESL       | Nop->Enter Idle after tRP                                      |      |  |

| ing                | L  | Н   | Н   | Н  | х         | NOP        | Nop->Enter Idle after tRP                                      |      |  |

|                    | L  | Н   | Н   | L  | х         | BST        | Nop->Enter Idle after tRP                                      |      |  |

|                    | L  | Н   | L   | Н  | BA,CA,A10 | READ/READA | ILLEGAL                                                        | 3    |  |

|                    | L  | Н   | L   | L  | BA,CA,A10 | WRIT/WRITA | ILLEGAL                                                        | 3    |  |

|                    | L  | L   | Н   | Н  | BA,RA     | ACT        | ILLEGAL                                                        | 3    |  |

|                    | L  | L   | Н   | L  | BA,A10    | PRE/PALL   | Nop->Enter Idle after tRP                                      |      |  |

|                    | L  | L   | L   | Н  | х         | REF/SELF   | ILLEGAL                                                        |      |  |

|                    | L  | L   | L   | L  | Op-Code   | MRS        | ILLEGAL                                                        |      |  |

| Row                | Н  | х   | х   | х  | х         | DESL       | Nop->Enter Row Active after tRCD                               |      |  |

| Activating         | L  | Н   | Н   | Н  | х         | NOP        | Nop->Enter Row Active after tRCD                               |      |  |

|                    | L  | Н   | Н   | L  | х         | BST        | Nop->Enter Row Active after tRCD                               |      |  |

|                    | L  | Н   | L   | Н  | BA,CA,A10 | READ/READA | ILLEGAL                                                        | 3    |  |

|                    | L  | Н   | L   | L  | BA,CA,A10 | WRIT/WRITA | ILLEGAL                                                        | 3    |  |

|                    | L  | L   | Н   | Н  | BA,RA     | ACT        | IILLEGAL                                                       | 3,7  |  |

|                    | L  | L   | н   | L  | BA,A10    | PRE/PALL   | ILLEGAL                                                        | 3    |  |

|                    | L  | L   | L   | Н  | х         | REF/SELF   | ILLEGAL                                                        |      |  |

|                    | L  | L   | L   | L  | Op-Code   | MRS        | ILLEGAL                                                        |      |  |

#### Operative command table 1 (Continued)

| Current<br>State      | হ্য | RAS | CAS | WE | Add       | Command                            | Action                           | Note   |

|-----------------------|-----|-----|-----|----|-----------|------------------------------------|----------------------------------|--------|

| Write                 | Н   | х   | x   | х  | х         | DESL                               | Nop->Enter Row Active after tDPL |        |

| Recover-<br>ing       | L   | Н   | Н   | Н  | х         | NOP                                | Nop->Enter Row Active after tDPL |        |

|                       | L   | Н   | Н   | L  | x         | BST                                | Nop->Enter Row Active after tDPL |        |

|                       | L   | Н   | L   | Н  | BA,CA,A10 | READ/READA                         | Start Read, Determine AP         | 4      |

|                       | L   | Н   | L   | L  | BA,CA,A10 | WRIT/WRITA                         | New Write, Determine AP          |        |

|                       | L   | L   | Н   | Н  | BA,RA     | ACT                                | ILLEGAL                          | 3      |

|                       | L   | L   | Н   | L  | BA,A10    | PRE/PALL                           | ILLEGAL                          | 3      |

|                       | L   | L   | L   | Н  | х         | REF/SELF                           | ILLEGAL                          |        |

|                       | L   | L   | L   | L  | Op-Code   | MRS                                | ILLEGAL                          |        |

| Write                 | Н   | Х   | х   | x  | х         | DESL                               | Nop->Enter Precharge after tDPL  |        |

| Recover-<br>ing with  | L   | Н   | Н   | Н  | х         | NOP                                | Nop->Enter Precharge after tDPL  |        |

| Auto                  | L   | Н   | Н   | L  | х         | BST                                | Nop->Enter Precharge after tDPL  |        |

| Precharge             | L   | Н   | L   | Н  | BA,CA,A10 | READ/READA                         | ILLEGAL                          | 3,4    |

|                       | L   | Н   | L   | L  | BA,CA,A10 | WRIT/WRITA                         | ILLEGAL                          | 3      |

|                       | L   | L   | н   | Н  | BA,RA     | ACT                                | ILLEGAL                          | 3      |

|                       | L   | L   | Н   | L  | BA,A10    | PRE/PALL                           | ILLEGAL                          | 3      |

|                       | L   | L   | L   | H  | х         | REF/SELF                           | ILLEGAL                          |        |

|                       | L   | L   | L   | L  | Op-Code   | MRS                                | ILLEGAL                          |        |

| Refresh-              | Н   | х   | х   | х  | Х         | DESL                               | Nop->Enter Idle after tRC        | 1      |

| ing                   | L   | Н   | Н   | x  | х         | NOP/BST                            | Nop->Enter Idle after tRC        |        |

|                       | L   | Н   | L   | X  | x         | READ/WRITE                         | ILLEGAL                          |        |

|                       | L   | L   | Н   | Х  | х         | ACT/<br>PRE/PALL                   | ILLEGAL                          |        |

|                       | L   | L   | L   | Х  | х         | REF/SELF/<br>MRS                   | ILLEGAL                          |        |

| Mode                  | Н   | х   | Х   | x  | Х         | DESL                               | Nop->Enter Idle after 2Clocks    |        |

| Register<br>Accessing | L   | Н   | Н   | Н  | х         | NOP                                | Nop->Enter Idle after 2Clocks    |        |

|                       | L   | Н   | Н   | L  | х         | BST                                | ILLEGAL                          | $\top$ |

|                       | L   | Н   | L   | x  | х         | READ/WRITE                         | ILLEGAL                          |        |

|                       | L   | L   | Х   | х  | х         | ACT/PRE/<br>PALL/ REF/<br>SELF/MRS | ILLEGAL                          |        |

#### Notes for "Operative command table 1,2,3"

- 1.H:High level, L:Low level, X:High or low level (Don't care), V:Valid data input

- 2.All entries assume that CKE was active(High level) during the preceding clock cycle.

- 3.Illegal to bank in specified states; Function may be legal in the bank indicated by Bank Address(BA), depending on the state of that bank.

- 4. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

- 5.If both banks are idle, and CKE is inactive(Low level), µPD4516XX will enter Power Down Mode. All input buffers except CKE will be disabled.

- 6.If both banks are idle, and CKE is inactive(Low level), µPD4516XXX will enter Self-Refresh mode. All input buffers except CKE will be disabled.

- 7.Illegal if tree is not satisfied.

- 8.Illegal if tras is not satisfied.

- 9.Must satisfy burst interrupt condition.

- 10. Must mask preceding data which don't satisfy ton.

- 11.Illegal if trop is not satisfied.

# Command truth table for CKE

| Current<br>State    | CKE<br>n-1 | CKE<br>n | ĊŚ | RAS | CAS | WE | Add     | Action                           | Note |

|---------------------|------------|----------|----|-----|-----|----|---------|----------------------------------|------|

| Self-               | Н          | X        | Х  | Х   | Х   | Х  | Х       | INVALID,CLK(n-1) would exit S.R  |      |

| Refresh<br>(S.R.)   | L          | Н        | Н  | X   | Х   | Х  | Х       | S.R. Recovery                    | 2    |

| (0.11.)             | L.         | Н        | L  | Н   | Н   | X  | X       | S.R. Recovery                    | 2    |

| :                   | L          | Н        | L  | Н   | L.  | Х  | Х       | ILLEGAL                          | 2    |

|                     | L          | Н        | L  | L   | х   | X  | Х       | ILLEGAL                          | 2    |

|                     | L          | L        | X  | X   | Х   | Х  | Х       | Maintain S.R.                    |      |

| Self-               | Н          | Н        | Н  | Х   | Х   | Х  | X       | Idle after tRC                   |      |

| Refresh<br>Recovery | Н          | Н        | L  | Н   | Н   | Х  | Х       | Idle after tRC                   |      |

|                     | Н          | Н        | L  | Н   | L   | Х  | х       | ILLEGAL                          |      |

|                     | Н          | Н        | L  | L   | X   | Х  | X       | ILLEGAL                          |      |

|                     | Н          | L        | Н  | Х   | Х   | Х  | Х       | Begin Clock Suspend next cycle   | 5    |

|                     | Н          | L        | L  | Н   | Н   | х  | х       | Begin Clock Suspend next cycle   | 5    |

|                     | Н          | L        | L  | Н   | L   | X  | Х       | ILLEGAL                          |      |

|                     | Н          | L        | L  | L   | Х   | X  | х       | ILLEGAL                          |      |

|                     | L          | Н        | Х  | X   | Х   | Х  | Х       | Exit Clock Suspend next cycle    | 2    |

|                     | L          | L        | Х  | X   | х   | ×  | х       | Maintain Clock Suspend           |      |

| Power               | Н          | X        | X  | X   | X   | X  |         | INVALID,CLK(n-1) would exit P.D. |      |

| Down<br>(P.D.)      | L          | Н        | X  | Х   | Х   | Х  | Х       | EXIT P.D>Idle                    | 2    |

| (1.5.)              | L          | L        | X  | Х   | Х   | Х  | х       | Maintain Power Down Mode         |      |

| Both                | Н          | Н        | Н  | X   | X   | X  |         | Refer to Operations in Table 1   |      |

| Banks Idle          | Н          | Н        | L  | Н   | X   | X  |         | Refer to Operations in Table 1   |      |

|                     | Н          | Н        | L  | L   | Н   | X  |         | Refer to Operations in Table 1   |      |

|                     | Н          | Н        | L  | L   | L   | Н  | Х       | Refresh                          |      |

|                     | Н          | Н        | L  | L   | L   | L  | Op-Code | Refer to Operations in Table 1   |      |

|                     | Н          | L        | Н  | Х   | Х   | Х  |         | Refer to Operations in Table 1   |      |

|                     | Н          | L        | L  | Н   | х   | Х  |         | Refer to Operations in Table 1   |      |

|                     | Н          | L        | L  | L   | Н   | X  |         | Refer to Operations in Table 1   |      |

|                     | Н          | L        | L  | L   | L   | Н  | Х       | Self Refresh                     | 3    |

|                     | H          | L        | L  | L   | L   | L  | Op-Code | Refer to Operations in Table 1   |      |

|                     | L          | X        | X  | X   | x   | x  | Х       | Power-Down                       | 3    |

| Any State           | Н          | Н        | X  | X   | X   | X  | х       | Refer to Operations in Table 1.  |      |

| other than          | Н          | L        | x  | X   | ×   | ×  | х       | Begin Clock Suspend next cycle   | 4    |

| above.              | L          | Н        | X  | X   | X   | X  | X       | Exit Clock Suspend next cycle    |      |

|                     | L          | 1        | X  | x   | x   | x  | х       | Maintain Clock Suspend.          |      |

#### Notes for "Command truth table for CKE"

- 1.H:High level, L:Low level, X:High or low level(Don't care)

- 2.CKE Low to High transition will re-enable CLK and other inputs asynchronously. A minimum setup time must be satisfied before any command other than EXIT.

- 3.Power-Down and Self-Refresh can be entered only from the Both Banks Idle

- 4.Must be legal command as defined in Operative command table 1.

- 5.Illegal if tsnex is not satisfied.

#### Command truth table for 2-bank operation

| CS | RAS | CAS | WE | ВА    | A10 | A9-0     | Action                  | "FROM" State     | "TO" State   |

|----|-----|-----|----|-------|-----|----------|-------------------------|------------------|--------------|

| Н  | х   | Х   | Х  | ×     | X   | х        | NOP                     | Any              | Any          |

| L  | Н   | Н   | Н  | х     | Х   | Х        | NOP                     | Any              | Any          |

| L  | Н   | Н   | L  | X     | x   | X        | BST                     | (R/W/A)0(I/A)1   | A0(I/A)1     |

|    |     |     |    | ļ     |     |          |                         | IO(I/A)1         | I0(I/A)1     |

|    |     |     |    |       |     |          |                         | (R/W/A)1(I/A)0   | A1(I/A)0     |

|    |     |     |    | ł     |     |          |                         | I1(I/A)0         | I1(I/A)0     |

| L  | Н   | L   | Н  | Н     | Н   | CA       | Read                    | (R/W/A)1(I/A)0   | RP1(VA)0     |

|    | 1   |     |    | Н     | Н   | CA       |                         | A1(R/W)0         | RP1A0        |

|    |     |     |    | Н     | L   | CA       |                         | (R/W/A)1(I/A)0   | R1(I/A)0     |

|    |     |     |    | Н     | L   | CA       | 1                       | A1(R/W)0         | R1A0         |

|    |     |     |    | L     | Н   | CA       | 1                       | (R/W/A)0(I/A)1   | RP0(I/A)1    |

|    |     |     |    | L     | Н   | CA       |                         | A0(R/W)1         | RP0A1        |

|    |     |     |    | L     | L   | CA       | 1                       | (R/W/A)0(I/A)1   | R0(I/A)1     |

|    |     | L   | L  | CA    |     | A0(R/W)1 | R0A1                    |                  |              |

| L  | Н   | L   | L  | Н     | Н   | CA       | Write                   | (R/W/A)1(I/A)0   | WP1(I/A)0    |

|    |     |     | İ  | Н     | Н   | CA       |                         | A1(R/W)0         | WP1A0        |

|    |     |     |    | Н     | L   | CA       |                         | (R/W/A)1(I/A)0   | W1(VA)0      |

|    |     |     |    | Н     | L   | CA       |                         | A1(R/W)0         | W1A0         |

|    |     |     |    | L     | Н   | CA       |                         | (R/W/A)0(I/A)1   | WP0(I/A)1    |

|    |     |     |    | L     | Н   | CA       | 1                       | A0(R/W)1         | WP0A1        |

|    |     |     | ]  | L     | L   | CA       | 7                       | (R/W/A)0(I/A)1   | W0(VA)1      |

|    |     |     |    | L     | L   | CA       |                         | A0(R/W)1         | W0A1         |

| L. | L   | Н   | Н  | Н     | RA  |          | Activate Row            | I1Any0           | A1Any0       |

|    |     |     | 1  | L     | RA  |          | 1                       | I0Any1           | A0Any1       |

| L  | L   | Н   | L  | ×     | Н   | X        | Precharge               | (R/W/A/I)0(I/A)1 | 1011         |

|    | 1   |     |    | X     | Н   | X        |                         | (R/W/A/I)1(I/A)0 | 1110         |

|    |     |     |    | Н     | L   | х        |                         | (R/W/A/I)1(I/A)0 | I1(I/A)0     |

|    |     |     |    | Н     | L   | Х        | 1                       | (I/A)1(R/W/A/I)0 | I1(R/W/A/I)0 |

|    |     |     |    | L     | L   | X        |                         | (R/W/A/I)0(I/A)1 | I0(I/A)1     |

|    |     |     |    | L     | L   | Х        |                         | (I/A)0(R/W/A/I)1 | 10(R/W/A/I)1 |

| L  | L   | L   | Н  | Х     | X   | Х        | Refresh                 | 1011             | 1011         |

| L  | L   | L   | L  | Op-Co | de  |          | Mode Register<br>Access | 1011             | 1011         |

Notes for "Command truth table for 2-bank operation"

Logic level abbreviations

H:High level, L:Low level, X:High or low level(Don't care)

Pin name abbreviation BA:Bank address (A11)

2.State abbreviations

I = Idle

I = Idle

A = Row active

R = Read with No precharge (No precharge is posted)

W = Write with No precharge (No precharge is posted)

RP = Read with auto precharge (Precharge is posted)

WP = Write with auto precharge (Precharge is posted)

Any = Any State

X0Y1 = Y1X0 = Bank0 is in state "X",Bank1 is in state "Y"

(XYY)0Z1 = Z1(X/Y)0 = Bank0 is in state "X"or"Y",Bank1 is in state "Z"

3.If the μPD4516XXX is in a state other than above listed in the "From State" column, the command is illegal.

4.The states listed under "To" might not be entered on the next clock cycle. Timing restrictions apply.

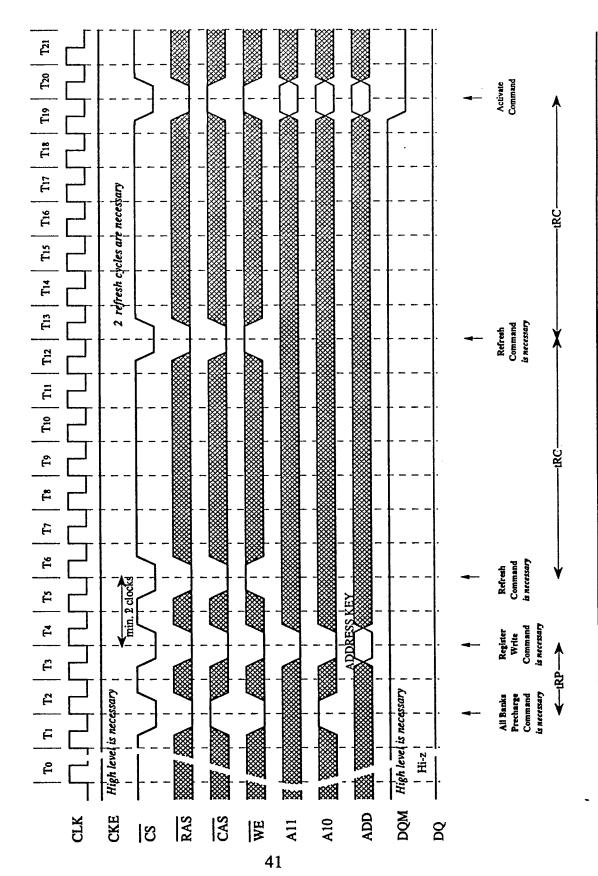

#### Initialization

Synchronous DRAM must be initialized in the power-on sequence, like conventional DRAMs. Once power has been applied, a 100 µs delay must precede any signals being toggled.

During this delay, CKE and DQM must be held high.

After the 100 µs delay, both banks must be precharged using the All Banks Precharge command. Once Precharge is completed and the minimum tap is satisfied, the Mode Register can be programmed.

Two clocks after the Mode Register Set command, two CBR Refresh command that satisfy the tac on on each CBR Refresh cycle must be performed.

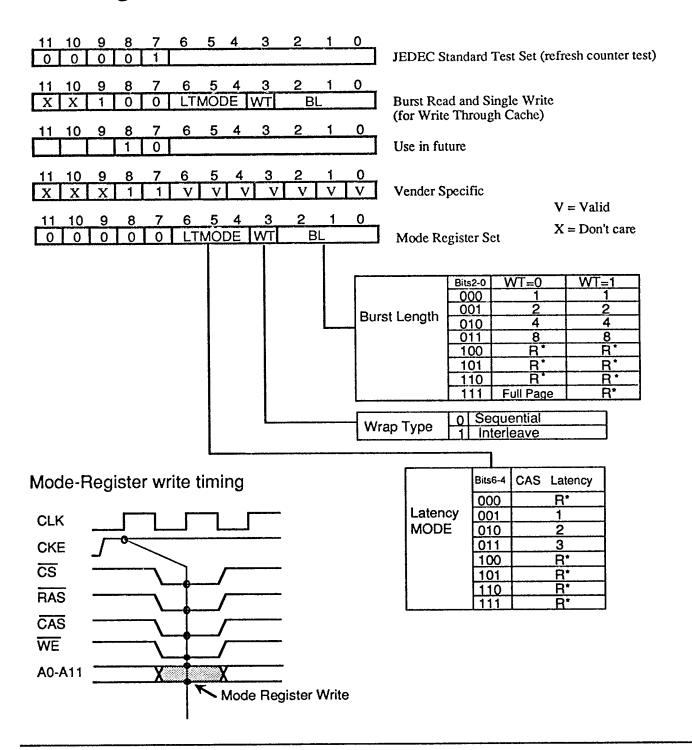

#### Programming the mode Register

The mode register is programmed by the Mode Register Set command using address bits A11 - A0 as data inputs. The register retains data until it is reprogrammed or the device loses power.

The mode register has four fields;

Options

A11 - A7

CAS latency A6 - A4

Wrap type A3

Burst length A2 - A0

After Mode Register programming, any command can not be asserted for at least two clocks.

# CAS Latency

CAS Latency is the most critical of the parameters being set. It tells the device how many clocks must elapse befor the data will be available. The NEC SDRAM is capable of reconfiguring its internal architecture based on the value of CAS Latency.

The value of determined by the frequency of the clock and the speed grade of the device. Table of page 39 shows the relationship of CAS Latency to the clock period and the speed grade of the device.

#### Burst Length

Burst Length is the number of words that will be output or input in read or write cycle. After a read burst has completed, the output bus will become high impedance.

The burst lengthis programmable as 1, 2, 4, 8 or full page.

#### Wrap Type(Burst Sequence)

The wrap type specifies the order in which the burst data will be addressed. This order is programmable as either "Sequential" or "Interleave". The method chosen will depend on the type of CPU in the system.

Some microprocessor cache system are optimized for sequential addressing and othrs for interleaved addressing. Table of the page 23 shows the addressing sequense for each burst length using them. Both sequences support burst of 1, 2, 4 and 8. Additionally , sequential sequence supports the full page length.

# **Mode-Register**

## Burst Length and Sequence

#### Burst of Two

| Starting Address<br>( column address<br>A0, binary ) | Sequential Addressing Sequence (decimal) | Interleave Addressing Sequence (decimal) |

|------------------------------------------------------|------------------------------------------|------------------------------------------|

| 0                                                    | 0, 1                                     | 0, 1                                     |

| 1                                                    | 1,0                                      | 1,0                                      |

#### Burst of Four.

| Starting Address<br>( column address<br>A1-A0, binary ) | Sequential Addressing<br>Sequence (decimal) | Interleave Addressing Sequence (decimal) |

|---------------------------------------------------------|---------------------------------------------|------------------------------------------|

| 00                                                      | 0, 1, 2, 3                                  | 0, 1, 2, 3                               |

| 01                                                      | 1, 2, 3, 0                                  | 1, 0, 3, 2                               |

| 10                                                      | 2, 3, 0, 1                                  | 2, 3, 0, 1                               |

| 11                                                      | 3, 0, 1, 2                                  | 3, 2, 1, 0                               |

#### Burst of Eight

| Starting Address<br>( column address<br>A2-A0, binary ) | Sequential Addressing Sequence (decimal) | Interleave Addressing Sequence (decimal) |

|---------------------------------------------------------|------------------------------------------|------------------------------------------|

| 000                                                     | 0,1,2,3,4,5,6,7                          | 0,1,2,3,4,5,6,7                          |

| 001                                                     | 1,2,3,4,5,6,7,0                          | 1,0,3,2,5,4,7,6                          |

| 010                                                     | 2,3,4,5,6,7,0,1                          | 2,3,0,1,6,7,4,5                          |

| 011                                                     | 3,4,5,6,7,0,1,2                          | 3,2,1,0,7,6,5,4                          |

| 100                                                     | 4,5,6,7,0,1,2,3                          | 4,5,6,7,0,1,2,3                          |

| 101                                                     | 5,6,7,0,1,2,3,4                          | 5,4,7,6,1,0,3,2                          |

| 110                                                     | 6,7,0,1,2,3,4,5                          | 6,7,4,5,2,3,0,1                          |

| 111                                                     | 7,0,1,2,3,4,5,6                          | 7,6,5,4,3,2,1,0                          |

Full page burst is an extension of the above tables of Sequential Addressing, with the length being 512 (for  $2M \times 8/9$  devices), 1024 (for  $4M \times 4$  device) and 256(for  $1M \times 16/18$  devices).

#### Address bits of Bank-Select and Precharge

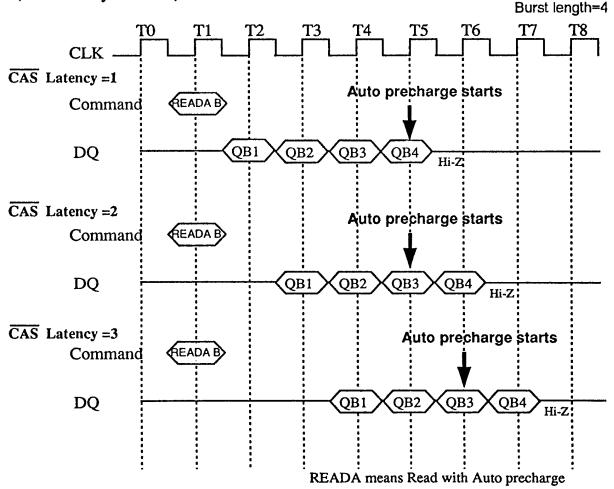

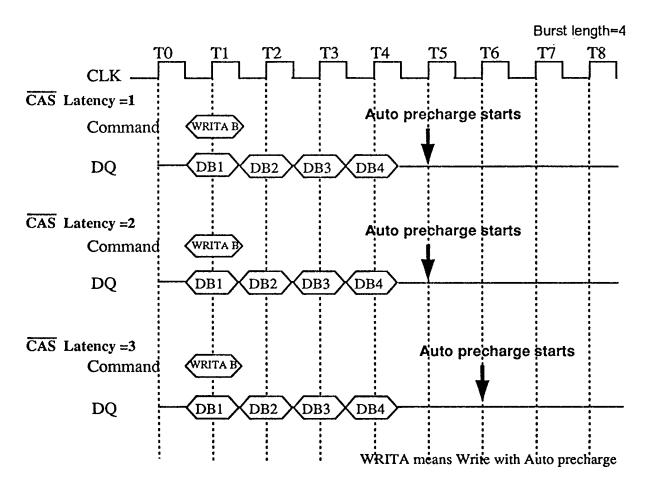

# Auto precharge

During a read or write command cycle, A10 controls whether auto precharge is selected. A10 high in the read or write command (Read with Auto precharge command or Write with Auto precharge command), auto precharge is selected and begins after the burst access automatically. In write cycle, the total must be satisfied to assert the next activate command to the bank being

precharged. And it is not necessary to know when the precharge starts.

When using auto precharge in read cycle, knowing when the precharge starts is important because the next activate command to the bank being precharge can not be executed until the precharge cycle ends. Once auto precharge has started, an activate command to the bank can be asserted after the has been satisfied.

The clock that begins the auto precharge cycle is depend on both the CAS latency programmed into the mode register and whether READ or WRITE cycle.

#### Read with Auto precharge

During READ cycle, the auto precharge begins on the clock that indicates the last data word output during the burst is valid (CAS latency of 1) or one clock earlier (CAS latency of 2 or 3).

#### Write with Auto precharge

During WRITE cycle, the auto precharge begins one clock after the <u>last</u> data word input to the device (<u>CAS</u> latency of 1 or 2) or two clocks after (<u>CAS</u> latency of 3).

In summary, the auto precharge cycle begins relative to a reference clock that indicates the last data word is valid.

In the table below, minus means clocks before the reference; plus means clocks after the reference.

| _ | CAS latency | Read | Write |  |

|---|-------------|------|-------|--|

|   | 1           | 0    | +1    |  |

|   | 2           | -1   | +1    |  |

|   | 3           | -1   | +2    |  |

# Read / Write Command Interval

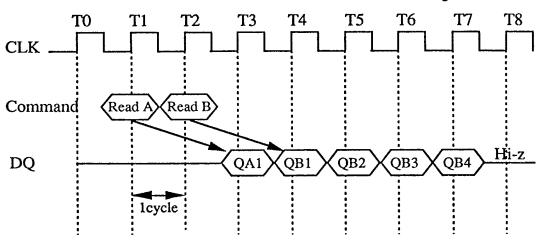

#### **Read to Read Command Interval**

During READ cycle, when new Read command is asserted, it will be effective after CAS Latency, even if the previous READ operation does not completed. READ will be interrupted by another READ.

The interval between the commands is minimum 1 cycle. Each Read command can be asserted in every clock without any restriction.

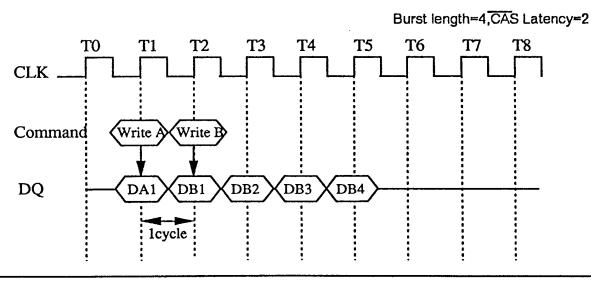

#### Write to Write Command Interval

During WRITE cycle, when new Write command is asserted, the previous burst will terminate and the new burst will begin with at new Write command. WRITE will be interrupted by another WRITE.

The interval between the commands is minimum 1. Each Write command can be asserted in every clock without any restriction.

Mar. 31 1994 ©NEC Corporation

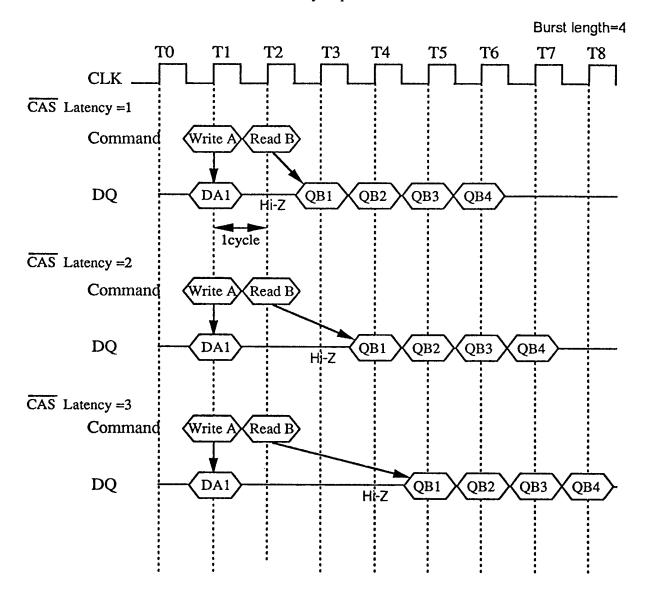

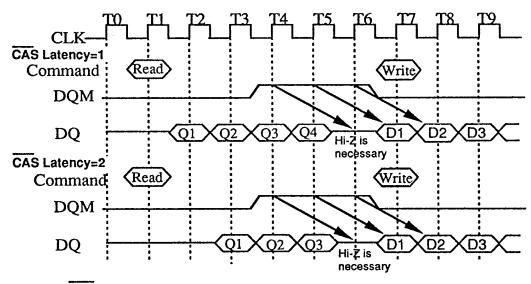

#### Write to Read command interval

Write command and Read command interval is also 1 cycle.

Only the write data before Read command will be written.

The data bus must be Hi-Z at least one cycle prior to the first Dout.

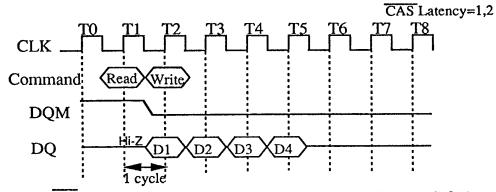

#### Read to Write Command Interval

During READ cycle, READ can be interrupted by WRITE. When the CAS Latency is 3 and then the burst length is Full page, the burst read can not be interrupted by WRITE. (A Burst Stop command(BST) or a Precharge command can interrupt).

When the CAS latency is 1 or 2, the Read and Write command interval is minimum 1 cycle. There is a restriction to avoid data conflict. The data bus must be Hi-Z using DQM before e WRITE.

In case CAS latency is 1 or 2, READ can be interrupted by WRITE. DQM must be High at least 3 clocks prior to the Write command.

Burst Length=8, CAS Latency=1, 2

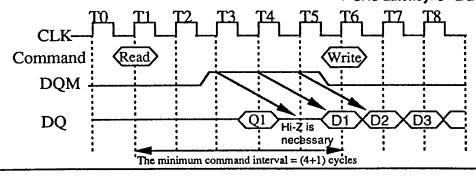

In case CAS latency is 3 (burst length is not Full page), READ can be interrupted by WRITE. The minimum command interval is [burst length + 1] cycles. DQM must be High at least 3 clocks prior to the Write command.

ex.) CAS Latency=3 Burst length=4

Mar. 31 1994 ©NEC Corporation

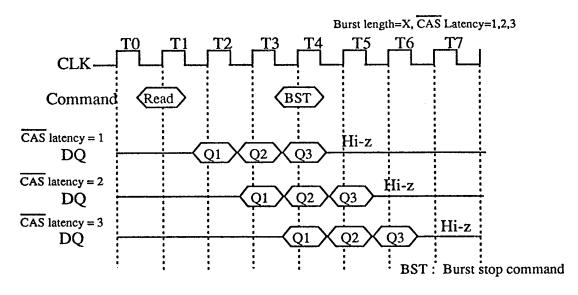

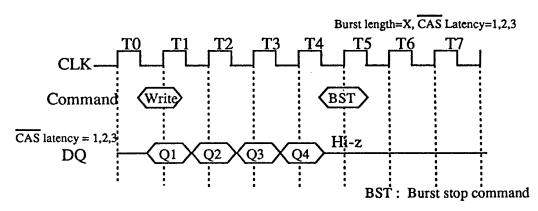

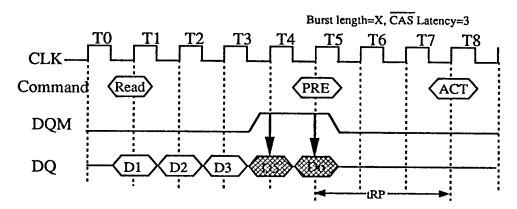

# **Burst termination**

There are two methods to terminate a burst operation other than using a read or a write command. One is the burst stop command and the other is the precharge command.

## **Burst stop command**

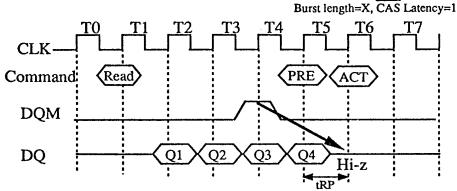

During the READ cycle, when the burst stop command is asserted, the burst read data are terminated and the data-bus goes to High-Z after the CAS latency from the burst stop command.

During the WRITE cycle, when the burst stop command is asserted, the burst read data are terminated and data-bus go to High-Z at the same clock with the burst stop command.

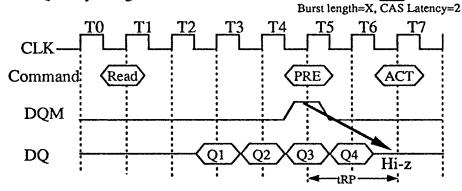

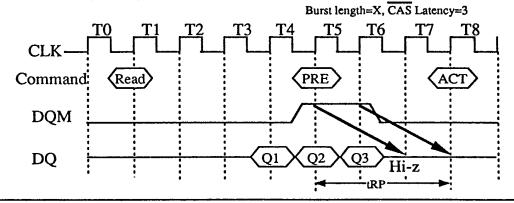

## Precharge termination

During the READ cycle, the burst read operation is terminated by a precharge command. When the precharge command is asserted, the burst read operation is terminated and precharge starts. The same bank can be activated again after tRP from the precharge command. The DQM must be high to mask the invalid data.

When CAS latency is 1, the read data will remain valid until the precharge command is asserted. Invalid data may appear one clock after valid data out.

The DQM may be high to mask the invalid data.

When CAS latency is 2, the read data will remain valid until one clock after the precharge command. Invalid data may appear one clock after valid data out.

The DQM may be high to mask the invalid data.

When CAS latency is 3, the read data will remain valid until one clock after the precharge command. Invalid data may appear one and two clocks after valid data out.

The DQM may be high to mask the invalid data.

Mar. 31 1994 © NEC Corporation

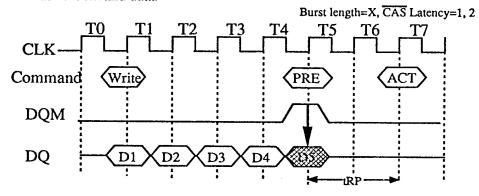

During the Write cycle, the burst write operation is terminated by a precharge command. When the precharge command is asserted, the burst write operation is terminated and precharge starts.

The same bank can be activated again after tRP from the precharge command.

The DQM must be high to mask invalid data in.

When CAS latency is 1 or 2, the write data written prior to the precharge command will be correctly stored.

However, invalid data may be written at the same clock as the precharge command. To prevent this from happening, DQM must be high at the same clock as the precharge command. This will mask the invalid data.

When CAS latency is 3, the write data written more than one clock prior to the precharge command will be correctly stored.

However, invalid data may be written at one clock before and the same clock as the precharge command.

To prevent this from happening, DQM must be high from one clock prior to the precharge command until the precharge command. This will mask the invalid data.

# Electrical Specifications ABSOLUTE MAXIMUM RATINGS

Voltage on Power Supply Pin Relative to GND -1.0 to +4.6 -1.0 to +4.6 Voltage on Input Pin Relative to GND ٧ 50 Short Circuit Output Current mA1 Power Dissipation w °° 0 to +70 Operating Temperature -55 to +125 Storage Temperature

\*COMMENT: Exposing the device to stress above those listed in absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

| PARAMETER                | SYMBOL | MIN. | TYP. | MAX. | UNIT |

|--------------------------|--------|------|------|------|------|

| Supply Voltage           | Vcc    | 3.0  | 3.3  | 3.6  | v    |

| High Level Input Voltage | VIH    | 2.0  |      | 4.6  | v    |

| Low Level Input Voltage  | VIL    | -0.3 |      | 0.8  | V    |

| Ambient Temperature      | Ta     | 0    |      | 70   | °C   |

| C CHARACTERISTICS                                  | 1 1     |                                                                                  | CAS          | L     |        | MAXI! |     |      | L.OTT |

|----------------------------------------------------|---------|----------------------------------------------------------------------------------|--------------|-------|--------|-------|-----|------|-------|

| PARAMETER                                          | SYMBOL  | TEST CONDITION                                                                   |              | GRADE | X4     | X8    | X16 | UNIT | NOTE  |

|                                                    |         |                                                                                  |              | -10   | 70     | 75    | 80  |      |       |

| Operating Current                                  |         |                                                                                  | CL=1         | -12   | 65     | 70    | 75  | mA.  | 3     |

|                                                    |         | Burst length = 1 tRC≥ tRC( MIN )                                                 | 102          | -13   | 60     | 65    | 70  | ] "" | ,     |

|                                                    |         |                                                                                  |              | -15   | 60     | 65    | 70  |      |       |

|                                                    | ١ ا     |                                                                                  |              | -10   | 75     | 80    | 85  |      |       |

|                                                    | Icc 1   | Io = 0 mA                                                                        |              | -12   | 70     | 75    | 80  | İ .  |       |

|                                                    |         |                                                                                  | CL=2         | -13   | -13 65 | 70    | 75  | mA   | 3     |

|                                                    |         |                                                                                  |              | -15   | 65     | 70    | 75  |      |       |

|                                                    |         |                                                                                  |              | -10   | 80     | 85    | 90  |      |       |

|                                                    |         |                                                                                  | CL=3         | -12   | 75     | 80    | 85  | ١    | 3     |

|                                                    |         |                                                                                  | CL=3         | -13   | 70     | 75    | 80  | mA   | ,     |

|                                                    |         |                                                                                  |              | -15   | 65     | 70    | 75  |      |       |

| rechargeStandby Current                            | Icc 2P  | CKE ≤ VIL (MAX) tCK= 15ns                                                        |              | 3     | 3      | 3     |     |      |       |

| in Power-down mode                                 | Icc 2PS | CKE≤VIL(MAX) tCK=∞                                                               |              | 2     | 2      | 2     | mA  |      |       |

| rechargeStandby Current<br>in Non power -down mode | Icc 2N  | CKE ≥ VIH (MIN) tCK= 15ns<br>CS ≥ VIH(MIN)<br>Input signals are changed one time | during 30ns. |       | 20     | 20    | 20  | mA   |       |

| in 140n power -down mode                           | Icc 2NS | OVE > VIII (AVDI) -OV                                                            |              |       | 6      | 6     | 6   |      |       |

| Active Standby Current                             | Icc 3P  | CKE ≤ VIL (MAX) tCK= 15ns                                                        |              |       | 3      | 3     | 3   | mA   |       |

| in Power-down mode                                 | Icc 3PS | CKE ≤ VIL (MAX) tCK= ∞                                                           |              |       | 2      | 2     | 2   | 1 "" |       |

| Active Standby Current                             | Icc 3N  | CKE ≥ VIH (MIN) tCK= 15ns<br>CS ≥ VIH(MIN)<br>Input signals are changed one time | during 30ns. |       | 25     | 25    | 25  | mA   |       |

| in Non power -down mode                            |         | CHARLES VILLA VILLA COM                                                          |              | 10    | 10     | 10    | ""  |      |       |

| DC CHARACTERIS                 | STICS (Reco | ommended Operating Conditions unless of | herwise noted) 2/2 | 2      |     |     |      |      |      |

|--------------------------------|-------------|-----------------------------------------|--------------------|--------|-----|-----|------|------|------|

| DADAN (PETER                   | 63/1/00/    |                                         | CASI               |        |     | MAX | OMUM |      |      |

| PARAMETER                      | SYMBOL      | TEST CONDITION                          | CAS Latency        | GRADE  | X4  | X8  | X16  | UNIT | NOTE |

|                                |             |                                         |                    | -10    | 70  | 75  | 90   |      |      |

|                                | CL= 1       | CL= 1                                   | -12                | 60     | 65  | 80  |      |      |      |

|                                |             |                                         | }                  | -13    | 55  | 60  | 75   |      |      |

|                                |             | ıCK ≥ ıCK (MIN)                         |                    | -15    | 55  | 60  | 75   |      |      |

| Operating Current (Burst Mode) | Icc 4       | Io = 0 mA                               |                    | -10    | 110 | 120 | 150  |      |      |

| (Daist Mode)                   |             |                                         | CL= 2              | -12    | 90  | 100 | 125  | mA   | 3    |

|                                |             |                                         |                    | -13    | 85  | 95  | 115  |      |      |

|                                |             |                                         |                    | -15    | 85  | 95  | 115  |      |      |

|                                |             |                                         |                    | -10    | 150 | 165 | 210  |      |      |

|                                |             | CL= 3                                   | -12                | 130    | 145 | 180 |      |      |      |

|                                |             |                                         | -13                | 120    | 130 | 160 |      |      |      |

|                                |             |                                         |                    | -15    | 100 | 110 | 140  |      |      |

| -                              |             |                                         | -10                | 90     | 90  | 90  |      |      |      |

|                                |             |                                         | CL= 1              | -12    | 80  | 80  | 80   |      |      |

|                                |             |                                         |                    | -13    | 75  | 75  | 75   |      |      |

|                                |             |                                         |                    | -15    | 75  | 75  | 75   |      |      |

| Refresh Current                | Icc 5       | tRC≥tRC(MIN)                            |                    | -10    | 95  | 95  | 95   |      |      |

|                                |             |                                         | CL= 2              | -12    | 85  | 85  | 85   | mA   |      |

|                                |             |                                         | CL-2               | -13    | 80  | 80  | 80   |      |      |

|                                |             |                                         |                    | -15    | 80  | 80  | 80   |      |      |

|                                |             |                                         |                    | -10    | 100 | 100 | 100  |      |      |

|                                |             |                                         |                    | -12    | 90  | 90  | 90   |      |      |

|                                |             |                                         | CL= 3              | -13    | 85  | 85  | 85   |      |      |

|                                |             |                                         |                    | -15 80 |     | 80  | 80   |      |      |

| Cals Dassala Ca                |             | CVF < 0.01                              |                    | .**    | 2   | 2   | 2    | mA   |      |

| Self Refresh Current           | Icc 6       | CKE≤0.2V                                |                    | -**L   | 100 | 100 | 100  | μА   |      |

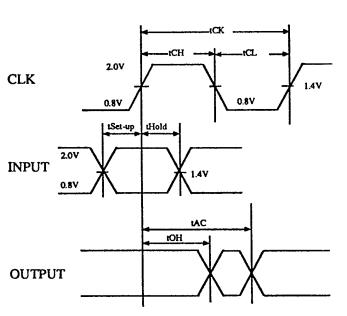

#### SYNCHRONOUS CHARACTERISTIC (Recommended Operating unless otherwise note)

| PARAMETER               |                       | SYMBOL | -1   |          | -1   |          |      | 3       |      | 15      | JNIT | NOTE |     |    |

|-------------------------|-----------------------|--------|------|----------|------|----------|------|---------|------|---------|------|------|-----|----|

|                         |                       |        | MIN. | MAX.     | MIN. | MAX.     | MIN. | MAX.    | MIN. | MAX.    |      |      | ŀ   | 3. |

|                         | CAS Latency = 3       | ıCK3   | 10   | (100MHz) | 12   | (83MFLz) | 13   | (75MHz) | 15   | (66MHz) | ns   |      | 3   | .5 |

| Clock Cycle Time        | CAS Latency = 2       | ıCK2   | 15   | (66MHz)  | 18   | (55MHz)  | 19.5 | (50MHz) | 19.5 | (50MHz) | ns   |      |     | l  |

|                         | CAS Latency = 1       | tCK1   | 30   | (33MHz)  | 36   | (28MHz)  | 39   | (25MHz) | 39   | (25MHz) | ns   |      | 3.4 | l  |

|                         | CAS Latency = 3       | tAC3   |      | 9        |      | 11       |      | 12      |      | 14      | ns   | 50PF |     | l  |

| Access Time from CLK    | CAS Latency = 2       | tAC2   |      | 12       |      | 15       |      | 16.5    |      | 16.5    | ns   | 80PF |     | l  |

|                         | CAS Latency = 1       | tACI   |      | 27       |      | 33       |      | 36      |      | 36      | ns   | 80pf |     | l  |

| CLK High Level Width    |                       | ıСН    | 3.5  |          | 4    |          | 5    |         | 5    |         | ns   |      |     | İ  |

| CLK Low Level Width     |                       | ıCL    | 3.5  |          | 4    |          | 5    |         | 5    |         | ns   |      | 3.4 | l  |

| Data-out Hold Time      |                       | tOH    | 4    |          | 4    |          | 4    |         | 4    |         | ns   |      |     | ĺ  |

| Data-out Low-Impedance  | Гіте                  | tLZ    | 0    | <u> </u> | 0    |          | 0    |         | 0    |         | ns   |      |     | l  |

| Data-out High Impedance | Time                  | ιHZ    | 0    | 10       | 0    | 10       | 0    | 10      | 0    | 10      | ns   |      |     | l  |

| Data-in Set-up Time     |                       | tDS    | 3    |          | 3.5  |          | 3.5  |         | 3.5  |         | ns   |      |     | l  |